HBM2E DFI Assertion IP

DFI HBM2E Assertion IP provides an efficient and smart way to verify the DFI HBM2E designs quickly without a testbench.

Overview

DFI HBM2E Assertion IP provides an efficient and smart way to verify the DFI HBM2E designs quickly without a testbench. The SmartDV's DFI HBM2E Assertion IP is fully complian with standard DFI HBM2E Specification.

HBM2E DFI Assertion IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

HBM2E DFI Assertion IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Specification Compliance

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports HBM2E devices compliant with JEDEC HBM2E DRAM Standard JESD235B and JESD235C.

- Supports all Interface Groups.

- Supports Write Transactions with Data mask

- Supports DRAM Clock disabling feature.

- Supports Data bit enable/disable feature.

- Supports 1:1, 1:2 and 1:4 MC to PHY frequency ratio.

- Supports frequency change protocol.

- Supports Low power control features.

- Supports Error signaling.

- Supports DFI Read/Write Chip Select.

- Supports all types of timing and protocol violations detection for timing parameters like tphy_wrlat ,tphy_wrdata,trd_dataen and tphy_rdlat delays

- Constantly monitors DFI behavior during simulation.

- Protocol checker fully compliant with DFI 4.0 or 5.0 Specifications.

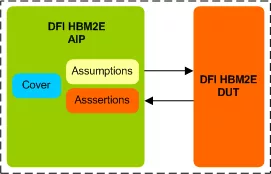

- Assertion IP features

- Assertion IP includes:

- System Verilog assertions

- System Verilog assumptions

- System Verilog cover properties

- Synthesizable Verilog Auxiliary code

- Support Master mode, Slave mode, Monitor mode and Constraint mode.

- Supports Simulation mode (stimulus from SmartDV HBM2E VIP) and Formal mode (stimulus from Formal tool).

- Rich set of parameters to configure HBM2E Assertion IP functionality.

Block Diagram

Benefits

- Runs in every major formal and simulation environment.

What’s Included?

- Detailed documentation of Assertion IP usage.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about HBM IP core

High Bandwidth Memory Evolution from First Generation HBM to the Latest HBM4

Breaking the HBM Bit Cost Barrier: Domain-Specific ECC for AI Inference Infrastructure

High Bandwidth Memory (HBM) at the AI Crossroads: Customization or Standardization?

Overcoming Timing Closure Issues in Wide Interface DDR, HBM and ONFI Subsystems

High Bandwidth Memory (HBM) Model & Verification IP Implementation - Beginner's guide

Frequently asked questions about LPDDR IP

What is HBM2E DFI Assertion IP?

HBM2E DFI Assertion IP is a HBM IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this HBM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this HBM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.