Verification IP for HBM

Comprehensive memory model and PHY verification HBM VIP is a comprehensive memory VIP solution portfolio for high bandwidth memor…

Overview

Comprehensive memory model and PHY verification

HBM VIP is a comprehensive memory VIP solution portfolio for high bandwidth memory (HBM), targeting a new standard in memory performance, density, power consumption, and cost. HBM VIP is intended for SoC and memory control ler designers who employ external HBM modules and PHY developers to ensure both comprehensive verification and protocol and timing compliance. Using a truly flexible and open architecture based on a 100% native SystemVerilog and UVM implementation, Avery HBM VIP implements a complete set of models and timing and protocol checkers.

Key features

- HBM2E, HBM3 memory models, HBM memory controller and DFI-PHY models

- Models support flexible and unencrypted timing class for customization, including random constraints for DRAM access times and self-refresh

- Supports power state management

- Injects errors at all layers through callbacks

- Comprehensive protocol and timing checks

- Tracker log monitors all levels and improves debug

- Sparse memory model

- Direct access to memory banks, MRS registers

- Backdoor access of memory and behavior injection

- Default memory value configuration

- Memory initialization from file ($readmemh)

- Supports all timing of JEDEC-defined speed bin and density

- Control/randomize DQS timing, jitter, and skew

- Detailed timing checks including jitter/skew and write/read DQS checks

- Quicksim modes

- Supports legacy and pseudo channel modes

- All normal HBM commands

- DM, ECC, and DBI functions DBI optional DDR commands

- Clock frequency change sequence (6.6)

- Target row refresh (TRR) mode (6.7)

- Temperature compensated refresh and CATTEMP modes (6.8)

- All IEEE 1500 port commands

- Interconnect redundancy remapping modes (6.9)

- HBM loopback test modes (6.10)

- Memory vendor support

- Timing parameters from SK and Samsung

- Performance metrics for all command-command latency including bank group analysis, utilization, and bandwidth

- Monitor mode to run with vendor memory model

- Timing and functional checks

- Command and data activities monitoring

- Bypass initialization

- Supports user-controlled license checkout at runtime

- 100% native SystemVerilog and UVM implementation

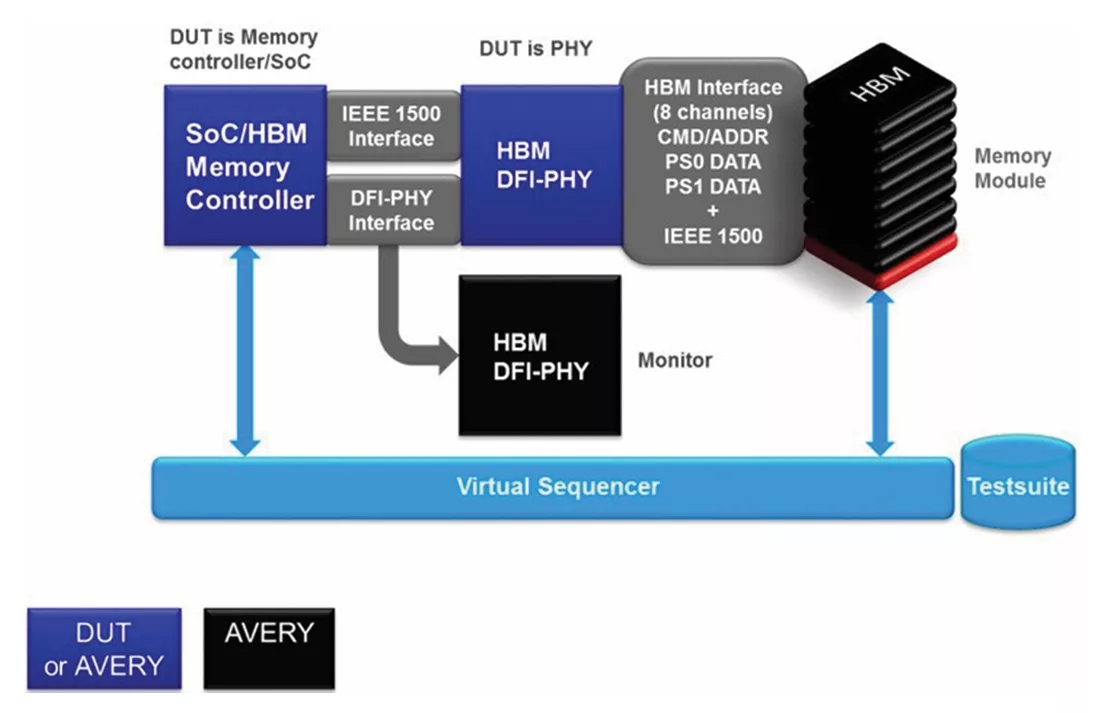

Block Diagram

Benefits

- Provides comprehensive memory VIP

- Includes complete models, timing, and protocol checkers

- Delivers the full range of DUT configurations

- Verifies PHYs, host mem ctrl IP, SoCs with mem ctrl

- Offers a flexible and open architecture

- Supports native SV/UVM implementation

What’s Included?

- PCIe Gen1-6 dual mode RC/EP, Retimer, and PIPE PHY and optional UCIe PHY driver BFMs

- Compliance test suites

- User guide

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about HBM IP core

High Bandwidth Memory Evolution from First Generation HBM to the Latest HBM4

Breaking the HBM Bit Cost Barrier: Domain-Specific ECC for AI Inference Infrastructure

High Bandwidth Memory (HBM) at the AI Crossroads: Customization or Standardization?

Overcoming Timing Closure Issues in Wide Interface DDR, HBM and ONFI Subsystems

High Bandwidth Memory (HBM) Model & Verification IP Implementation - Beginner's guide

Frequently asked questions about LPDDR IP

What is Verification IP for HBM?

Verification IP for HBM is a HBM IP core from Siemens Digital Industries Software listed on Semi IP Hub.

How should engineers evaluate this HBM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this HBM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.