HBM 4 Verification IP

The HBM4 Verification IP provides an effective & efficient way to verify the components interfacing with HBM interface of an ASIC…

Overview

The HBM4 Verification IP provides an effective & efficient way to verify the components interfacing with HBM interface of an ASIC/FPGA or SoC. The HBM4 VIP is fully compliant with Standard HBM Version JESD270-4 specifications from JEDEC. This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design time and the simulation time.

Key features

- Compliant to JEDEC HBM4 SDRAM Specification version JESD270-4

- Supports connection to any HBM Memory Controller IP communicating with a JESD270-4 compliant HBM Memory Model

- Reports various timing error signals, which can be used to check for any timing errors

- Provides full control to the user to enable/disable various types of messages

- Integrates easily in any verification environment

- Supports full timing models or bus functional models

- Multiple instances of Monitor can be instantiated in a Verification Environment to support multiple Stacks

- Supports advanced System Verilog features like constrained random testing

- Supports Callback / User Configuration in Monitor, Controller and Memory Model BFMs

- Supports a wide variety of Error Injection scenarios

- Supports Independent channel functioning

- Support stacks of either 4, 8, 12 or 16 DRAM dies

- Available in Channel Density of 3Gb to 16Gb

- Support 64 DQ width + ECC/SEV pins/per channel

- Support Up to 32 channels/device

- Support 16, 32, 48, or 64 banks per channel

- Supports Data Bus Inversion (DBIac) Feature

- Supports Parity Checking for Command/Address bus & Data bus

- Supports configurable timing parameters and Channels-Die associations

- Supports capturing all the valid HBM Row & Column commands including Activate, Read, Write, Precharge, Refresh,… in semi-independent way

- Supports Power-up Reset and initialization sequences

- Supports Power-Down, Self-Refresh operation

- Support Refresh Management, Adaptive Refresh Management, Directed Refresh Management

- Support Round rules for Row Access Timing

- Support On-die Dram ECC

- Support Write DCA Training, Read DCA Training, WDQS-to-CK Alignment Training, Rx Offset Calibration Training

- Supports IEEE testport feature, Loopback Test Mode

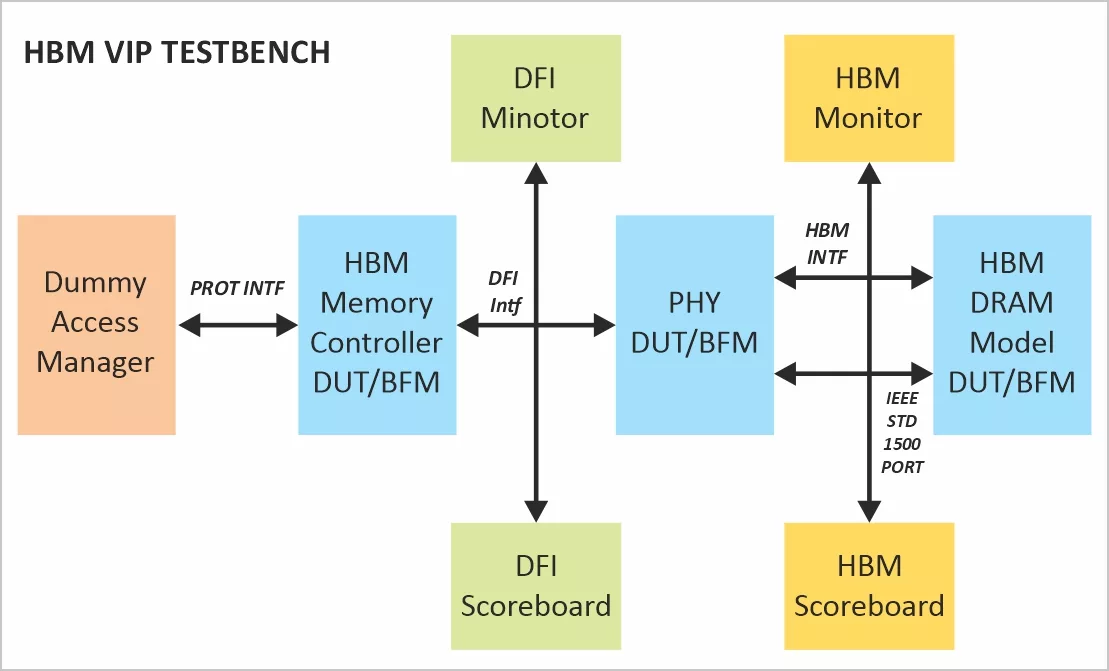

Block Diagram

Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog.

- Unique development methodology to ensure highest levels of quality.

- Availability of Compliance & Regression Test Suites

- 24X5 customer support.

- Unique and customizable licensing models.

- Exhaustive set of assertions and cover points with connectivity example for all the components.

- Consistency of interface, installation, operation and documentation across all our VIPs.

- Provide complete solution and easy integration in IP and SoC environment.

What’s Included?

- HBM Controller BFM

- HBM DRAM

- HBM Monitor and Scoreboard

- HBM PHY BFM Model

- HBM PHY Monitor and Scoreboard

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Integration Guide, User Manual and Release Notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about HBM IP core

High Bandwidth Memory Evolution from First Generation HBM to the Latest HBM4

Breaking the HBM Bit Cost Barrier: Domain-Specific ECC for AI Inference Infrastructure

High Bandwidth Memory (HBM) at the AI Crossroads: Customization or Standardization?

Overcoming Timing Closure Issues in Wide Interface DDR, HBM and ONFI Subsystems

High Bandwidth Memory (HBM) Model & Verification IP Implementation - Beginner's guide

Frequently asked questions about LPDDR IP

What is HBM 4 Verification IP?

HBM 4 Verification IP is a HBM IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this HBM?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this HBM IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.