GDDR6 PHY

High-performance IP for graphics, AI/ML, and automotive products The silicon-proven GDDR6 PHY and controller IP showcase -edge BE…

Overview

High-performance IP for graphics, AI/ML, and automotive products

The silicon-proven GDDR6 PHY and controller IP showcase leading-edge BER, BIST, and RAS capabilities. GDDR6 offers significantly more performance than the fastest speed of DDR5 at a moderate cost, making it ideal for high-bandwidth applications. Cadence’s unique, single-vendor GDDR6 IP solution speeds up integration and reduces interoperability risk.

Key features

- Single configuration supports one GDDR6 device per channel (coplanar) or two GDDR6 devices per channel (clamshell)

- DFI PHY Independent Mode for initialization and training

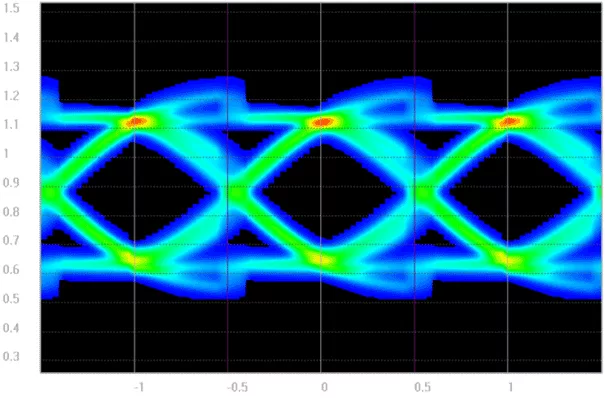

- Adaptive and continuous timing recovery

- Internal and external datapath loop-back modes

- Transmit crosstalk cancelation of immediate neighbors

- Per-bit DFE, CTLE, and FFE equalization

Block Diagram

What’s Included?

- Fully-characterized hard macro (GDSII)

- Complete design views

- Full documentation

Specifications

Identity

Provider

Learn more about GDDR IP core

SPAD: Specialized Prefill and Decode Hardware for Disaggregated LLM Inference

High Bandwidth Memory Evolution from First Generation HBM to the Latest HBM4

Designing the AI Factories: Unlocking Innovation with Intelligent IP

Breaking the Memory Bandwidth Boundary. GDDR7 IP Design Challenges & Solutions

The Growing Importance of AI Inference and the Implications for Memory Technology

Frequently asked questions about GDDR IP

What is GDDR6 PHY?

GDDR6 PHY is a GDDR IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this GDDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GDDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.