GDDR6 DFI Assertion IP

DFI GDDR6 Assertion IP provides an efficient and smart way to verify the DFI GDDR6 designs quickly without a testbench.

Overview

DFI GDDR6 Assertion IP provides an efficient and smart way to verify the DFI GDDR6 designs quickly without a testbench. The SmartDV's DFI GDDR6 Assertion IP is fully complian with standard DFI GDDR6 Specification.

GDDR6 DFI Assertion IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

GDDR6 DFI Assertion IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Specification Compliance

- Compliant with DFI version 4.0 or 5.0 Specifications.

- Supports GDDR6 devices compliant with JEDEC GDDR6 SGRAM Standard JESD250A and JESD250B.

- Supports GDDR6 x16 or x8 clamshell modes.

- Can be configured as a single controller driving two x16 GDDR6 channels simultaneously (x32 total) or two controllers each driving one x16 GDDR6 channel.

- Supports GDDR6 operation at up to 18Gbps.

- Supports GDDR6 error detection code (EDC).

- Supports controller retries read and write transactions after EDC error detected.

- Supports GDDR6 data bus inversion (DBI) and CA bus inversion (CABI).

- Supports Per-bank and All-bank refresh.

- Supports Write Single Mask (WSM) and Write Double Mask (WDM).

- Supports GDDR6 low power modes (self-refresh and power-down).

- Support for GDDR6 device densities from 8 to 32Gb.

- Supports automatic generation and user-controlled initialization sequences.

- Supports read and write commands with or without auto-precharge.

- Supports DRAM Clock disabling feature.

- Supports Low power control features.

- Supports Error signaling.

- Supports CA Training.

- Supports WCK-DQ Training.

- Supports WCK2CK Leveling.

- Supports RDQS Toggle mode.

- Supports all types of timing and protocol violations detection for timing parameters.

- Constantly monitors DFI behavior during simulation.

- Protocol checker fully compliant with DFI 4.0 or 5.0 Specifications.

- Assertion IP features

- Assertion IP includes:

- System Verilog assertions

- System Verilog assumptions

- System Verilog cover properties

- Synthesizable Verilog Auxiliary code

- Support Master mode, Slave mode, Monitor mode and Constraint mode.

- Supports Simulation mode (stimulus from SmartDV GDDR6 VIP) and Formal mode (stimulus from Formal tool).

- Rich set of parameters to configure GDDR6 Assertion IP functionality.

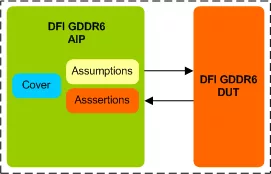

Block Diagram

Benefits

- Runs in every major formal and simulation environment.

What’s Included?

- Detailed documentation of Assertion IP usage.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about GDDR IP core

SPAD: Specialized Prefill and Decode Hardware for Disaggregated LLM Inference

High Bandwidth Memory Evolution from First Generation HBM to the Latest HBM4

Designing the AI Factories: Unlocking Innovation with Intelligent IP

Breaking the Memory Bandwidth Boundary. GDDR7 IP Design Challenges & Solutions

The Growing Importance of AI Inference and the Implications for Memory Technology

Frequently asked questions about GDDR IP

What is GDDR6 DFI Assertion IP?

GDDR6 DFI Assertion IP is a GDDR IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this GDDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GDDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.