GDDR7 Memory Controller

The GDDR7 controller IP core is designed for use in applications requiring high memory throughput including artificial intelligen…

Overview

The GDDR7 controller IP core is designed for use in applications requiring high memory throughput including artificial intelligence/machine learning (AI/ML), graphics, high-performance computing (HPC).

It supports 160 Gigabytes per second (GB/s) throughput for a GDDR7 memory device enabling next-level performance for AI accelerators and GPUs using GDDR7 memory.

How a GDDR7 Memory Controller Implementation in a Subsystem works

The GDDR7 controller supports all GDDR7 link features including PAM3 and NRZ signaling. Optimized for high efficiency and low latency across a wide variety of traffic scenarios, it offers low-power support (self-refresh, hibernate self-refresh, dynamic frequency scaling, etc.) and Reliability, Availability and Serviceability (RAS) features such as end-to-end data path parity, parity protection for stored registers, etc. Comprehensive memory test support and integration support for third-party PHYs are available.

Key features

- Supports up to 40 Gbps per pin operation

- 2.5 GHz CK4 clock

- 1.25 GHz controller clock

- Internal data path 32x memory width (i.e. 256 bits for 8-bit memory)

- Optimized for high efficiency and low latency across a wide range of traffic scenarios (random/sequential, short/long bursts, etc.)

- Optimized command sequence for highest bus utilization including per-bank refresh scheduling: single queue structure handles look-ahead activates/ precharges and read/write ordering for minimal latency

- Up to 4 AXI ports per channel

- Async or sync to core memory controller (lower latency for sync configuration)

- Multiple interface data width options (128, 256, 512)

- Up to 2 local ports per channel

- Supports low power modes

- Power-down

- Self-refresh, hibernate self-refresh

- Dynamic frequency scaling (DFS)

- Sleep

- Progressive low power

- Supports all GDDR7 link features

- CRC with retry for reads and writes

- PAM3 and NRZ signaling

- Data scramble

- Data poison

- Clamshell mode

- DQ logical remap

- Advanced RAS features

- End-to-end data path parity

- Parity protection for all stored registers

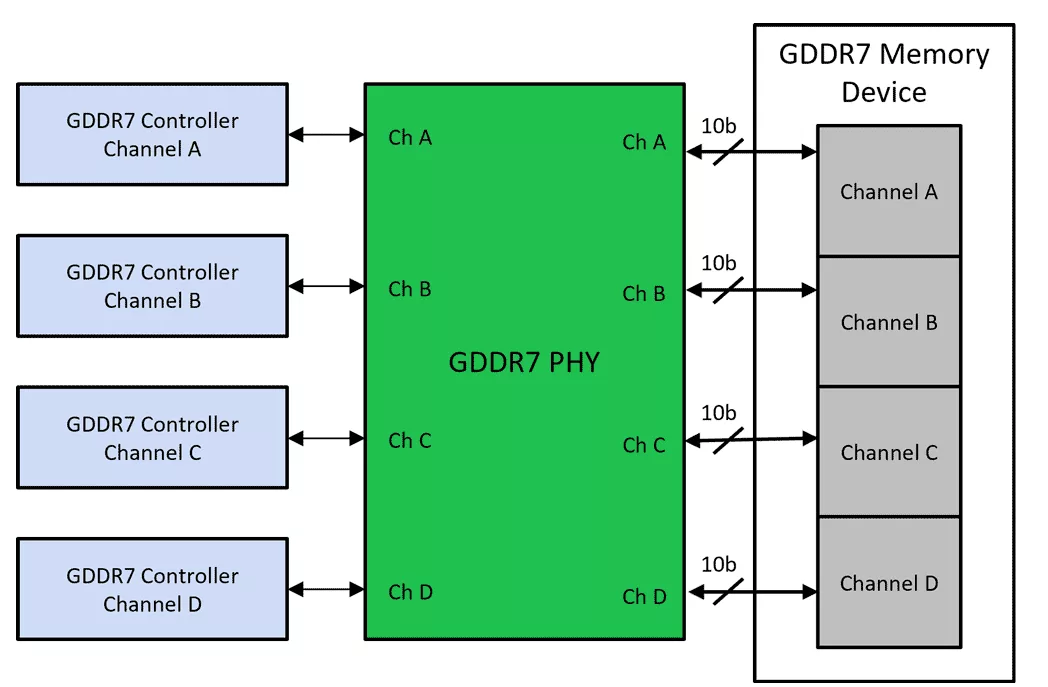

Block Diagram

Applications

- AI,

- Graphics,

- HPC

What’s Included?

- Core (source code)

- Testbench (source code)

- Complete documentation

- Expert technical support

- Maintenance updates

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about GDDR IP core

Micro-threaded Row and Column Operations in a DRAM Core

HBM4 Elevates AI Training Performance To New Heights

Selection Criteria for Using DDR, GDDR or MobileDDR Memories in System Designs

SPAD: Specialized Prefill and Decode Hardware for Disaggregated LLM Inference

High Bandwidth Memory Evolution from First Generation HBM to the Latest HBM4

Frequently asked questions about GDDR IP

What is GDDR7 Memory Controller?

GDDR7 Memory Controller is a GDDR IP core from Rambus, Inc. listed on Semi IP Hub.

How should engineers evaluate this GDDR?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this GDDR IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.