Verification IP for CXL

Accelerated confidence in simulation-based verification of RTL designs with Compute Express Link (CXL) interfaces: CXL1, CXL2, CX…

Overview

Accelerated confidence in simulation-based verification of RTL designs with Compute Express Link (CXL) interfaces: CXL1, CXL2, CXL3, CXL3.1

Avery CXL and PCI Express VIP provides a comprehensive verification solution featuring an advanced UVM environment that incorporates constrained random traffic generation, robust CXL/TL/DLL/PHY layer controls and error injection, protocol checks and coverage, functional coverage, protocol analyzer-like features for debugging, and performance analysis metrics. With the advanced capabilities of Avery VIP, engineers can work more efficiently, develop more complex tests, and work on more complex topologies, such as bifurcation. Avery compliance test suites offer effective core-through-chip-level tests, including those used in compliance workshops, as well as extended tests developed by Avery to cover specification features.

Key features

- Comprehensive CXL and PCIe standards support, including:

- CXL 1.1 + Errata, CXL 2.0, CXL 3.0

- LPIF

- CXS

- CPI/SFI

- PCIe 6.0

- PIPE 6.0, UCIe 1.0

- Host, device, switch, PHY, PIPE2PIPE, and RDI2RDI interfaces

- Host BFM features:

- Automatic bus enumeration and configuration of the CXL hierarchies

- Supports memory mapped registers (RCRB and MEMBAR0 region)

- Contains home agent with snooper filter of unlimited size

- Host memory of unlimited size

- Device BFM features

- Host-managed device memory of unlimited size

- Configured as Type1, Type2, and Type3 device

- Compliance checklist coverage to isolate DUT bugs faster

- Protocol analyzer debugging trace files

- Compliance test suites

- Common BFM features:

- Supports PCIe Gen5 with alternate protocol negotiation to CXL

- Supports PCIe mode and CXL mode for CXL.IO, CXL.Mem and CXL.Cache traffic

- Unified user application data class for both PCIe and CXL

- Realistic traffic arbitration among CXL.IO, CXL.Cache, CXL. Mem and CXL packets

- Contains requester agent with embedded cache

- Supports CXL cache coherency

- Highly randomized and configurable operation

- Provides callbacks and simplified APIs for tests writing

- User-customizable way of FLIT packing

- Supports full cache coherent load/store operations

- Supports automatic credit-based CXL data flow control

- Supports sync header bypass

- Supports CXL virtual LSM state machines

- Supports CXL link layer

- Supports CXL power management

- Support CXL reset mechanisms

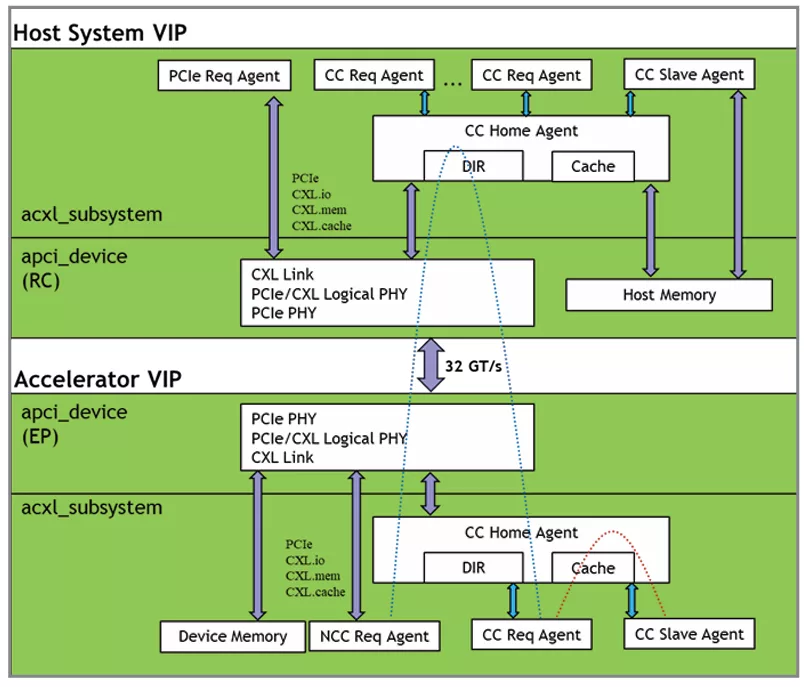

Block Diagram

Benefits

- Provides a comprehensive UVM verifica tion solution

- Boosts verification efficiency

- Enables development of more complex tests and more complex topologies

- Increases effectiveness with core through-chip-level tests

- Generates tracker reports showing packet flow

- Isolates compliance issues with compre hensive protocol checking, including protocol checklist coverage

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CXL IP core

Powering Up Efficiency: A Deep Dive into CXL L0p and its Verification

Demystifying CXL Memory Interleaving and HDM Decoder Configuration

From GPUs to Memory Pools: Why AI Needs Compute Express Link (CXL)

cMPI: Using CXL Memory Sharing for MPI One-Sided and Two-Sided Inter-Node Communications

Boosting AI Performance with CXL

Frequently asked questions about CXL IP cores

What is Verification IP for CXL?

Verification IP for CXL is a CXL IP core from Siemens Digital Industries Software listed on Semi IP Hub.

How should engineers evaluate this CXL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CXL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.