CXL 4.0/3.2/3/2 Verification IP

The CXL Verification IP provides an effective & efficient way to verify the components interfacing with CXL interface of an IP or…

Overview

The CXL Verification IP provides an effective & efficient way to verify the components interfacing with CXL interface of an IP or SoC. The CXL VIP is fully compliant with latest CXL specifications. This VIP is a light weight with an easy plug-and-play interface so that there is no hit on the design cycle time.

Key features

- Compliant with the CXL 3.2, 2.0 & 1.1 Specification.

- Support for all three protocols CXL.IO, CXL.CACHE & CXL.MEM including all CXL device types

- Support for PCIE Mode & Alternate Protocol Negotiation for CXL Mode

- Support for 256B flit in 64GT/s with PCIe Gen 6 as well as 32/16/8 GT/s speeds with backward compatibility.

- Support for different CXL/PCIe Resets.

- Support for CPI v1.0 (CXL-CACHE/MEM Protocol Interface), CXS B (Credited eXtensible Stream), LPIF v1.1 (Logical PHY Interface) and PIPE v6.2.

- Support for block level verification.

- Support for SerDes PIPE Architecture as well as Original PIPE Architecture.

- Configurable PIPE width support:

- Original PIPE Arch. - 8, 16, 32, 64

- SerDes PIPE Arch. - 10, 20, 40, 80.

- Support for CXL.IO throttling.

- Support for NOP insertion hint performance optimization.

- Support for Low Pin Count Interface as well as Legacy PIPE Interface.

- Support for CXL Retry Mechanism.

- Support for 68B and 256B flit structure.

- Support for CXL 3.2 Configuration and Memory Mapped Registers (For CXL Device and Ports).

- Support for CXL ALMP transmission and reception to control virtual link state machine and power state transition requests.

- Support for CXL ACK forcing & Link Layer Credit exchange mechanism.

- Support for Arbitration among the CXL.IO, CXL.CACHE and CXL.MEM packets with Interleaving of traffic between different CXL protocols.

- Support for randomization and user controllability in flit packing.

- Support for power management including the low power L1 with sub-state and L2.

- Support for CXL in band control message with CXL 3.2. (Viral & Poison)

- Support for Credit exchange field within 256B flit.

- Support for all 3 coherency models HDM-D, HDM-H and HDM-DB to access HDM memory.

- Support for PBR TLP for CXL.IO

- Support for Back Invalidate transactions.

- Support for RAS error logging & Signalling.

- Support for Extended Metadata.

- Support for Bogus, Viral, Global Persistent Flush and Data Object Exchange.

- Support for IDE.

- Support for QOS telemetry for memory.

- Provides two types of routing mechanism. (HBR and PBR).

- Provides a comprehensive user API (callbacks).

- Provides two types of 256B flits mechanism (Standard 256B flit & Lopt 256B flit).

- Provide Compliance test support.

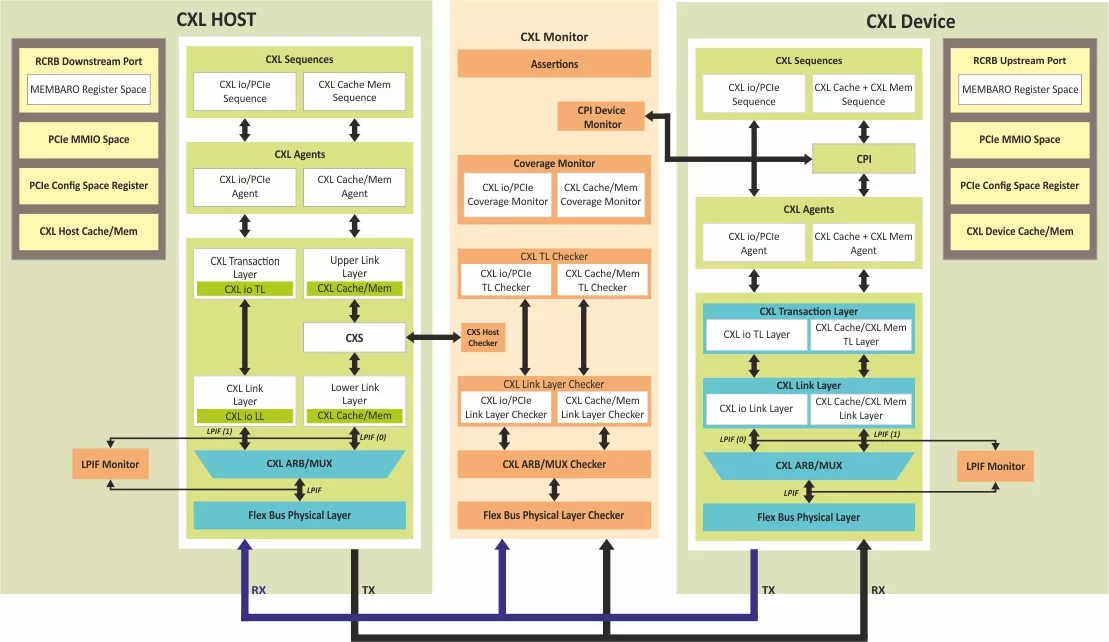

Block Diagram

Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog.

- Unique development methodology to ensure the highest levels of quality.

- 24X5 customer support.

- Unique and customizable licensing models.

- Exhaustive set of assertions, cover points with connectivity example for all the components.

- Consistency of interface, installation, operation, and documentation across all our VIPs.

- Provide complete solution and easy integration in IP and SoC environment.

- On-the-fly protocol checking using protocol check functions, static and dynamic assertion.

- Provides a comprehensive user API (callbacks).

- Graphical analyzer for easy debugging, regression analysis, performance, statistics and charts.

What’s Included?

- CXL Host/Device

- CXL Switch

- CXL BFM/Agents for:

- Host and Device sequences

- Transaction layer(CXL.IO and CXL.cache, CXL.mem)

- Link layer(CXL.IO and CXL.cache, CXL.mem)

- Arbiter/Mux layer

- PHY layer

- CXL Monitor and Scoreboard

- Test Environment & Test Suite:

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Cover Point Tests

- Compliance Tests

- Documents:

- Integration Guide

- User Manual

- Quick Start Guide, Release Notes

- FAQs

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about CXL IP core

Powering Up Efficiency: A Deep Dive into CXL L0p and its Verification

Demystifying CXL Memory Interleaving and HDM Decoder Configuration

From GPUs to Memory Pools: Why AI Needs Compute Express Link (CXL)

cMPI: Using CXL Memory Sharing for MPI One-Sided and Two-Sided Inter-Node Communications

Boosting AI Performance with CXL

Frequently asked questions about CXL IP cores

What is CXL 4.0/3.2/3/2 Verification IP?

CXL 4.0/3.2/3/2 Verification IP is a CXL IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this CXL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CXL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.