Simulation VIP for CXL

The Cadence® Verification IP (VIP) for Compute Express Link (CXL) is part of the Cadence family of VIP for PCI Express® (PCIe®).

Overview

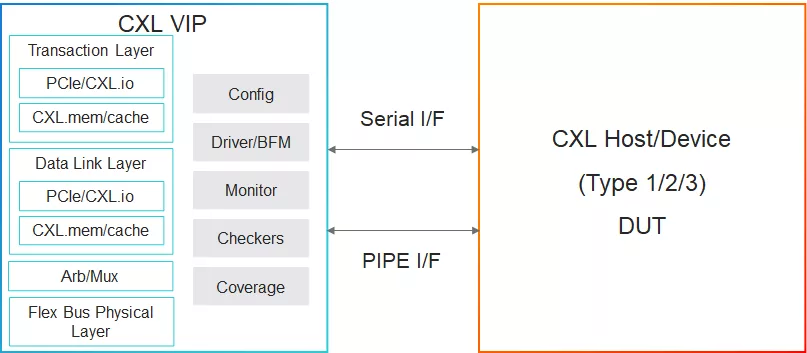

The Cadence® Verification IP (VIP) for Compute Express Link (CXL) is part of the Cadence family of VIP for PCI Express® (PCIe®). Built on top of Cadence's mature industry-leading VIP for PCIe, the CXL VIP provides a complete bus functional model for all three CXL protocols, CXL.io/CXL.mem/CXL.cache, and allows users to verify both CXL host and device designs for all device types (Type 1 – 3) from the very first days of the CXL protocol.

Designed for easy integration in testbenches at the IP, system-on-chip (SoC), and system level, the VIP for CXL runs on all simulators and supports SystemVerilog along with the widely adopted Universal Verification Methodology (UVM). This enables verification teams to reduce the time spent on environment development, and redirect it to cover a larger verification space, accelerate verification closure, and ensure end-product quality.

With a layered architecture and powerful callback mechanism, verification engineers can verify CXL features at each functional layer (PHY, link, transport, and application layer) and create highly targeted designs while taking advantage of the latest design methodologies for random testing to cover a larger verification space. The VIP for CXL can be used as a standalone and as a platform for running TripleCheck tests and supports the latest PIPE specification.

Supported specifications: Compute Express Link Specification 2.0 revision 1.0 and 3.0 revision 1.0.

Key features

- Device Configuration

- Host, Device

- Spec Version

- 1.1, 2.0, 3.0

- Device Type

- Type 1: Caching Devices/Accelerators: CXL.io, CXL.cache

- Type 2: Accelerators with Memory: CXL.io, CXL.cache, CXL.mem

- Type 3: Memory Buffers: CXL.io, CXL.mem

- Protocol Support

- CXL.io, CXL.mem, CXL.cache

- Interface

- Serial (NRZ, PAM4) and PIPE 5.x, PIPE 6.x

- Link Rate

- Native support of 64GT/s, 32 GT/s, and downgraded support of 16GT/s and 8GT/s

- Link Width

- Native widths (x16, x8, x4) and degraded widths (x2, x1)

- Downstream Port Support

- Root complex integrated endpoint (RCiEP) for CXL 1.1 and EP for CXL 2.0

- Register Space

- Configuration space registers (CXL DVSEC)

- Control status registers (CXL 2.0 DVSEC)

- CXL RCRB support for 1.1 backward compatibility testing

- FLIT Support

- CXL 3.0 256B Flit

- 64B Flit

- NULL flit

- CXL.io transaction mapping in FLIT

- CXL.mem/cache protocol FLIT

- CXL.mem/cache control FLIT: RETRY, LLCRD, INIT

- NOP Flit

- Flex Bus Support

- Alternative Protocol Support

- Framing and packet layout

- Framing error handling

- Physical Layer Latency Optimization (Sync Header Bypass)

- Arb/MUX

- vLSM/ALMP Low Power

- Deepest Allowable Power Management (DAPM)

- Weighted round-robin

- Arbitration bypass mode

- ALMP/vLSM bypass

- Enumeration

- CXL 1.1 and 2.0 enumeration

- Bypass enumeration

- Auto-enumeration for CXL DVSEC and Memory Mapped register space

- CXL.io

- Configuration space registers

- Memory-mapped registers

- Memory type indication on ATS

- PM messages, credits, and initialization

- PM VDM

- Deferrable Memory Write (DMWr) ECN

- CXL.mem

- M2S Req/RwD

- S2M NDR/DRS

- M2S Req/S2M NDR, DRS (Type 2 flow)

- Forward progressing rules

- Speculative memory read

- Memory error reporting

- QoS telemetry

- CXL.cache

- D2H request/response

- H2D request/response

- Back-Invalidation Snoops (CXL3.0 feature)

- Host, Device Bias modes

- Cache and Snoop filter modelling

- Mem/Cache Link Layer

- CXL 3.0, 2.0/1.1 Flit Slots support

- Initialization (LLINIT)

- Retry flow (RRSM, LRSM) for CXL 2.0

- Retry flow integration with PCIe 6.0 for CXL 3.0

- ACK/LLCRD forcing

- Viral and Poison support

- Integrity and Data Encryption (IDE)

- CXL.io/CXL.mem/CXL.cache encryption

- Authentication: DOE/SPDM/CMA for Discovery, Negotiation, Device attestation, Key negotiation, Bypass mode, Containment and Skid mode

- Error handling

- CXL 2.0 ECNs

- Devices Operating in CXL 1.1 mode with no RCRB

- System Plugins

- System-level scoreboard

- System Performance Analyzer

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CXL IP core

Powering Up Efficiency: A Deep Dive into CXL L0p and its Verification

Demystifying CXL Memory Interleaving and HDM Decoder Configuration

From GPUs to Memory Pools: Why AI Needs Compute Express Link (CXL)

cMPI: Using CXL Memory Sharing for MPI One-Sided and Two-Sided Inter-Node Communications

Boosting AI Performance with CXL

Frequently asked questions about CXL IP cores

What is Simulation VIP for CXL?

Simulation VIP for CXL is a CXL IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this CXL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CXL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.