GENZ VIP

GENZ Verification IP provides an smart way to verify the GENZ bi-directional bus.

Overview

GENZ Verification IP provides an smart way to verify the GENZ bi-directional bus. The SmartDV's GENZ Verification IP is fully compliant with GENZ specification and provides the following features.

GENZ VIP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

GENZ VIP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports GENZ Core specification 1.0 and 1.1.

- Supports GENZ Physical layer specification 1.0 and 1.1.

- Supports GENZ Fabric Management specification 1.0.

- Supports Byte-addressable memory access.

- Supports Block and Object storage access.

- Supports I/O device access.

- Supports all types of Messaging.

- Supports Accelerators access.

- Supports memory semantic communications using a packet-based transport to exchange operations that access a component’s resources.

- Supports non-memory applications including I/O, storage and message passing communications.

- Supports aggressive packet retransmission policies.

- Supports abstract physical layer interface enabling support of multiple physical layer implementations and media that can be tailored to solution-specific needs.

- Supports Ethernet physical layer as per IEEE 802.3-2015 specification.

- Supports PAM4-50G Fabric and PAM4-50G Local.

- Supports PCIe physical layer as per PCI Express Base specification 4.0 and 5.0.

- Supports Solution-driven packaging and Point-to-point topology.

- Supports real-time dynamic physical signaling rate, interface width and link width adjustment to meet workload or environmental conditions.

- Supports Advanced requests, e.g. atomics, buffer movement, pattern matching, etc. as well as transparent support for vendor-defined operations.

- Supports following CRCs based packet data integrity combined with transparent end-to-end packet error recovery.

- PCRC

- ECRC.

- Supports Flit encoding.

- Supports up to 32 virtual channels for each interface.

- Supports transparent transient error recovery and in-order packet delivery across a link through Link-Level Reliability (LLR).

- Supports Strong Ordering Domain Communications (SOD).

- Supports Vendor-defined Operations.

- Supports reliable Delivery and Error Handling.

- Supports Sequential Execution and Unordered Execution.

- Supports Physical Layer Abstraction.

- Supports end-to-end Multicast and Unicast communication.

- Supports Flow control.

- Supports Congestion and Deadline.

- Supports Address Translation.

- Supports Logical PCIe device.

- Supports Data striping.

- Supports Packet Alignment.

- Supports Symmetric and Asymmetric interfaces and links.

- Supports Memory Media RAS.

- Supports all Opclasses and Packet types.

- Supports Sanitize and Erase (SE).

- Supports Enqueue and Dequeue functionality.

- Supports high level security through following

- Anti-Replay Tag (ART)

- HMAC Code Calculation

- Interface Access Key

- Page R-Key

- Authentication Encryption (AEAD).

- Supports API structure for proposed interface.

- Supports general view of fabric’s management stack.

- Configurable timers and timeouts.

- Automated Error Injections at all layers.

- Supports RAR ACK and Proxy dependency.

- Checkers verify protocol timing checks and functional accuracy at each layer.

- Notifies the testbench of significant events such as transactions, warnings, timing and protocol violations.

- GENZ Verification IP comes with complete test suite to test every feature of GENZ specification.

- Functional coverage for complete GENZ features.

- Callbacks in BFM’s and Monitor for various events.

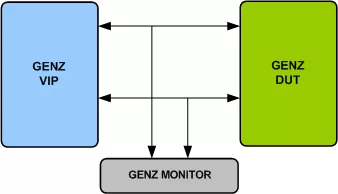

Block Diagram

Benefits

- Faster testbench development and more complete verification of GENZ designs.

- Easy to use command interface simplifies testbench control and configuration of Host,Device and monitor.

- Simplifies results analysis.

- Integrates easily into OpenVera, SytemVerilog, SystemC, Verilog.

- Runs in every major simulation environment.

What’s Included?

- Complete regression suite containing all the GENZ testcases.

- Examples showing how to connect various components, and usage of BFM and Monitor.

- Detailed documentation of all class, task and function's used in verification env.

- Documentation also contains User's Guide and Release notes.

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about CXL IP core

Powering Up Efficiency: A Deep Dive into CXL L0p and its Verification

Demystifying CXL Memory Interleaving and HDM Decoder Configuration

From GPUs to Memory Pools: Why AI Needs Compute Express Link (CXL)

cMPI: Using CXL Memory Sharing for MPI One-Sided and Two-Sided Inter-Node Communications

Boosting AI Performance with CXL

Frequently asked questions about CXL IP cores

What is GENZ VIP?

GENZ VIP is a CXL IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this CXL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this CXL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.