UFS 3.0 G4 Host Controller IE and UniPro

The Universal Flash Storage (UFS) Host Controller IP is a standard-based serial interface engine for implementing the JEDEC UFS i…

Overview

The Universal Flash Storage (UFS) Host Controller IP is a standard-based serial interface engine for implementing the JEDEC UFS interface in compliance with the JEDEC UFS, UFS Host Controller Interface (UFSHCI) standards as well as the UFS removable card v1.1 standards. The UFS Host Controller IP, compliant with the latest UFS v4.0 standard, is a high-performance, low-power interface that is primarily used in applications where data is stored on embedded or removable non-volatile mass storage memory devices. The UFS Host Controller IP integrates the UFS host controller application layer with a pre-configured MIPI® UniPro protocol stack that is optimized for UFS host applications.

Given the sensitive data stored on many mobile devices, smartphones in particular, robust security is an important consideration. The UFS Host Controller IP was designed with robust security features. To meet the demand for encryption of data stored on the smartphone’s local storage (contacts, e-mails, etc.), inline encryption (IE) has been added to the UFSHCI specification. The implementation of the AES-XTS encryption/decryption block, supporting 128- and 256-bit keys, is part of the data pipeline, ensuring transparency without any performance loss as it does not take any additional CPU cycles. In addition, Replay Protected Memory Block (RPMB) ensures that device memory regions can only be accessed by authenticated host applications. The Host Controller supports the necessary commands and data structures.

A standard-based synchronous bus system, such as AXI, connects the IP to the rest of the system-on-chip (SoC). This bus is connected to the register interface and the Direct Memory Access (DMA) interface of the IP. The register and data structure implementation is based on the UFSHCI specification and is used by the UFS Host Controller’s DMA engine. Leveraging industry standards in the UFS Host Controller ensures compatibility and performance.

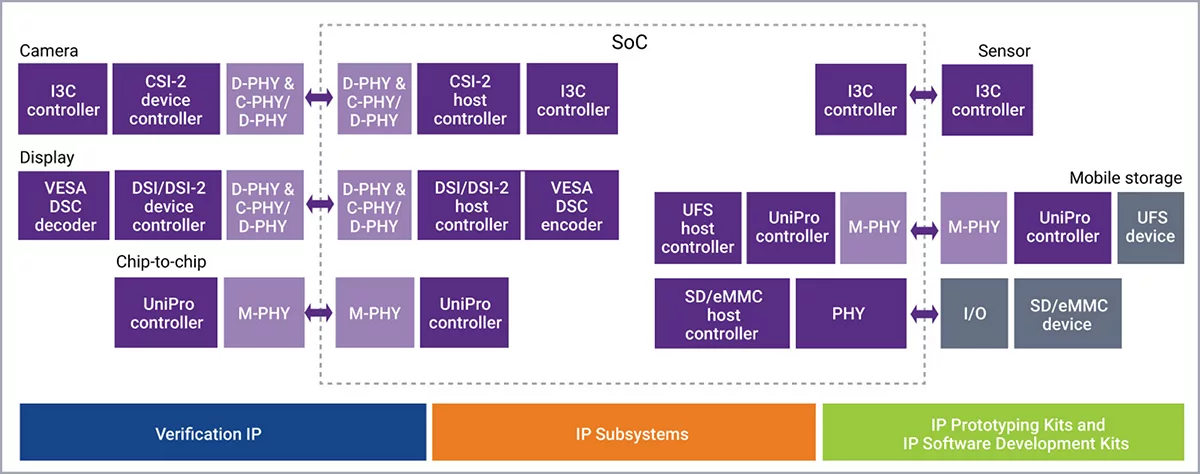

When the UFS Host Controller IP is combined with the MIPI® UniPro Controller IP and the MIPI M-PHY IP, the vendor provides a single vendor UFS IP solution that designers can easily integrate into application processors with less risk, while speeding time-to-market of advanced SoCs and device integrated circuits (ICs).

Key features

- Compliant with the JEDEC UFS, UFSHCI v4.0 and UFS card v1.1 standards

- Enables data and privacy protection using Inline Encryption (AES-XTS) and RPMB

- Delivered as UFS host application layer integrated with Synopsys MIPI UniPro v2.0 Controller IP

- Manages UFS protocol between host and external UFS device

- Single traffic class

- Supports M-PHY v5.0 and access to M-PHY attributes

- Supports multiple lanes (up to 2) and speed up to HS-Gear5

- Low-power operation, small area, and low latency

- Supports clock and power gating using Unified Power Format (UPF)

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UFS Controller IP core

The Future of Storage: From eMMC to the Blazing Speeds of UFS 5.0

Leveraging UVM based UFS Test Suite approach for Accelerated Functional Verification of JEDEC UFS IP

UFS or NVMe in Smartphone? See Apple's answer!

UFS Goes Mainstream

eMMC: The Embedded Storage Powering On-Device AI

Frequently asked questions about UFS Controller IP

What is UFS 3.0 G4 Host Controller IE and UniPro?

UFS 3.0 G4 Host Controller IE and UniPro is a UFS Controller IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this UFS Controller?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UFS Controller IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.