ONFI IO v5.0, 2.4GT/s, TSMC 12FFC, 1.2V, N/S orientation, H&V cell

ONFI I/O is a non-volatile memory interface technology with high bandwidth capabilities, mainly developed for flash storage appli…

Overview

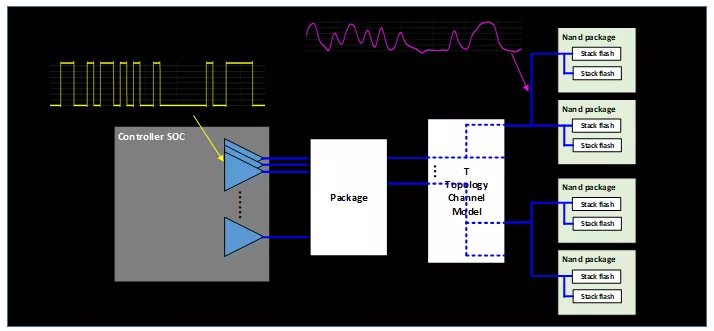

ONFI I/O is a non-volatile memory interface technology with high bandwidth capabilities, mainly developed for flash storage applications. M31 provides a silicon-proven ONFI I/O in a variety of process nodes, which complies with international Open NAND Flash Interface specification, providing on-die termination (ODT) and supporting ZQ impedance calibration, and can be customized based on customer specifications. The ONFI 6.0, ONFI 5.1, and ONFI 5.0 I/O IP have been silicon-proven at advanced FinFet nodes. In addition, M31 also provides solutions for signal integrity (SI) issues such as FFE and DFE.

Key features

- Supports ONFI 6.0(4.8Gbps), ONFI 5.1(3.6Gbps), ONFI 5.0(2.4Gbps), ONFI 4.1(1.2Gbps), ONFI 4.0(800Mbps) & ONFI 3.2(533Mbps)

- Power-sequence free

- Provides multi-driving-strength selection

- Provides CTT mode and LTT mode

- Provides two receivers (Schmitt trigger and LVCMOS receiver) in a cell, which can be selected by the register.

- Provides ODT (On-Die Termination)

- Provides ZQ Calibration

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 12nm | FFC | — |

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is ONFI IO v5.0, 2.4GT/s, TSMC 12FFC, 1.2V, N/S orientation, H&V cell?

ONFI IO v5.0, 2.4GT/s, TSMC 12FFC, 1.2V, N/S orientation, H&V cell is a Single-Protocol PHY IP core from M31 Technology Corp. listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.