AES-XTS encryption/decryption IP

SphinX is designed to accommodate the speed, latency and throughput requirements of high performance computer systems main memory…

Overview

SphinX is designed to accommodate the speed, latency and throughput requirements of high performance computer systems main memory / DRAM. The IP implements the standard (NIST FIPS 197) AES cipher in XTS mode (IEEE Std 1619-2018). The SphinX family of cores covers a scalable IP with 128b and 256b key support, allowing the designer to choose the most efficient and effective core that satisfies the latency and throughput requirements.

The design is fully synchronous and supports independent, non-blocking encryption/decryption at main memory speed. SphinX is available for immediate licensing.

References:

IEEE Std 1619-2018, IEEE Standard for Cryptographic Protection of Data on Block-Oriented Storage Devices https://standards.ieee.org/standard/1619-2018.html

NIST FIPS 197, Advanced Encryption Standard (AES) https://www.nist.gov/publications/advanced-encryption-standard-aes

Key features

- AES-XTS mode

- 128b and 256b key support

- High speed (@DDR4/DDR5 speed)

- High throughput (@DDR4/DDR5 throughput)

- Low latency

- Independent, non-blocking encryption/decryption at main memory speed

- Modular and scalable architecture

- Key expansion integrated

- Fully synchronous

- Optional bypass mode

- Standard compliance (NIST FIPS 197) AES cipher in XTS mode (IEEE Std 1619-2018)

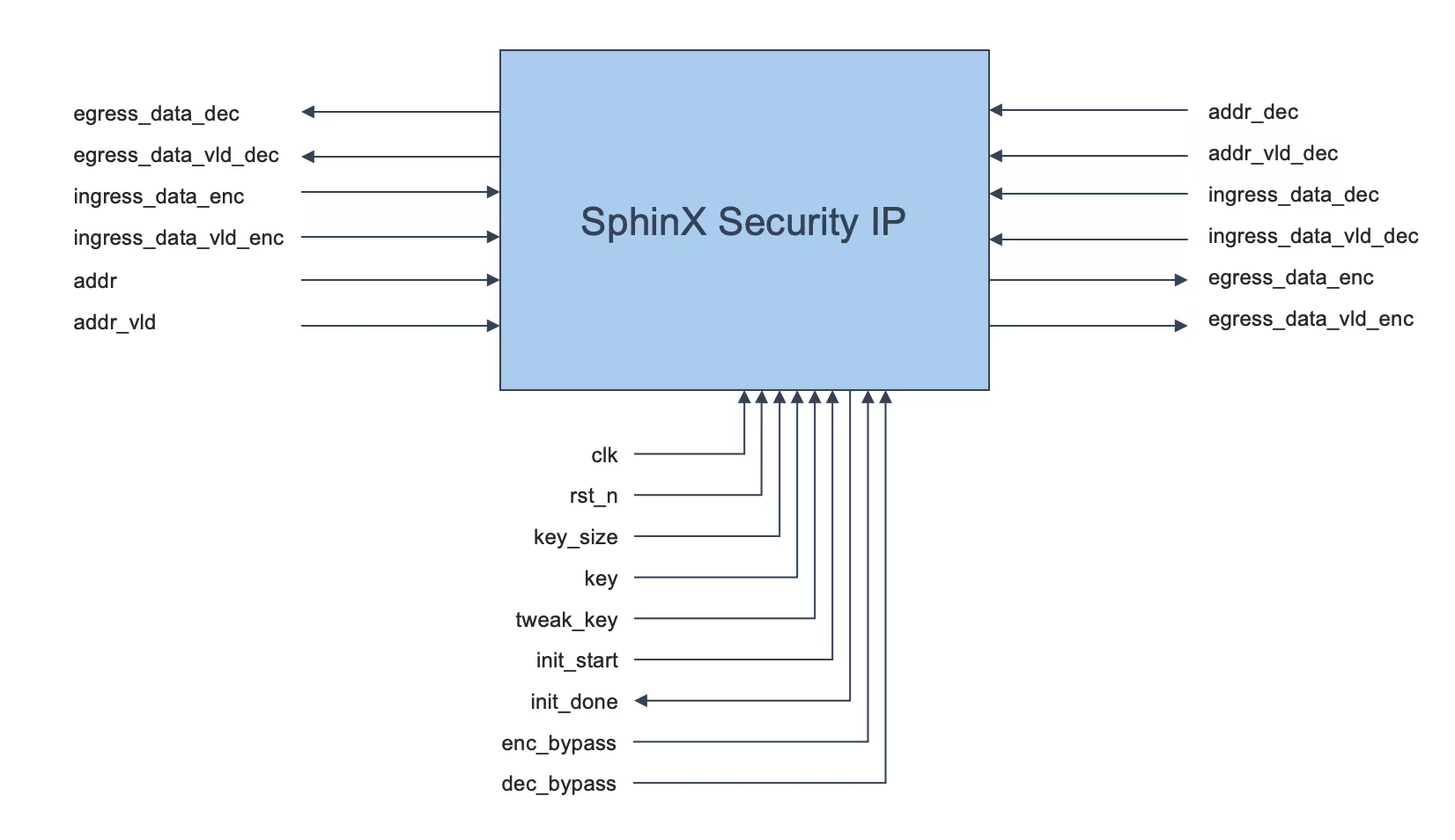

Block Diagram

Benefits

- Main memory encryption/decryption (@DDR4/DDR5 speed)

- Independent non-blocking encryption and decryption

- No additional memory required

- Fully pipelined design, optimized for high throughput and low latency

- Operating at main memory speed and throughput (DDR4/DDR5)

Applications

- Main memory (DDR4/DDR5) and other high performance storage devices such as NvMe, SSD, Optane and PCIe connected devices.

- Server

- Desktop

- AI

- ML

- Edge & Cloud

- Media & Entertainment

- Memory & Storage

- Automotive

- Defense

What’s Included?

- Synthesizable Verilog RTL (encrypted)

- Implementation constraints

- UVM testbench (self-checking)

- Vectors for testbench and expected results

- User Documentation

Specifications

Identity

Security

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Symmetric Crypto IP core

CXL - The Latest Specification in Secured Network Traffic

Securing your apps with Public Key Cryptography & Digital Signature

RoT: The Foundation of Security

Tailoring Root Of Trust Security Capabilities To Specific Customer Needs

Symmetric Cryptographic Offload Options for SoC Designers

Frequently asked questions about Symmetric Cryptography IP cores

What is AES-XTS encryption/decryption IP?

AES-XTS encryption/decryption IP is a Symmetric Crypto IP core from ZeroPoint Technologies AB listed on Semi IP Hub.

How should engineers evaluate this Symmetric Crypto?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Symmetric Crypto IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.