Verification IP for AMBA

AMBA® ACE and CHI coherent interconnect technologies enable an entirely new class of high-performance datacenter applications in …

Overview

AMBA® ACE and CHI coherent interconnect technologies enable an entirely new class of high-performance datacenter applications in areas of machine learning, network processing, storage off-load, in-memory database, and 4G/5G wireless technology. Processor architectures and accelerators can now seamlessly operate over cache coherent intercon nects using the right combination of general-purpose processors and heterogeneous acceleration devices, such as FPGAs, GPUs, network/ storage adapters, intelligent networks, and custom ASICs.

Avery AMBA VIP provides a comprehensive verification solution featuring an advanced UVM environment that incorporates constrained random traffic generation; robust packet, link, physical layer controls, and error injection; protocol checks, coverage, and functional coverage; protocol analyzer-like features for debugging; and performance analysis metrics. With the advanced capabilities of Avery VIP, you can work more effi ciently, develop more complex tests, and work on more complex topolo gies, such as multi-path, multi-link solutions. Avery compliance test suites offer effective core-through-chip-level tests, including those used in compliance workshops as well as extended tests developed by Avery to cover specification features.

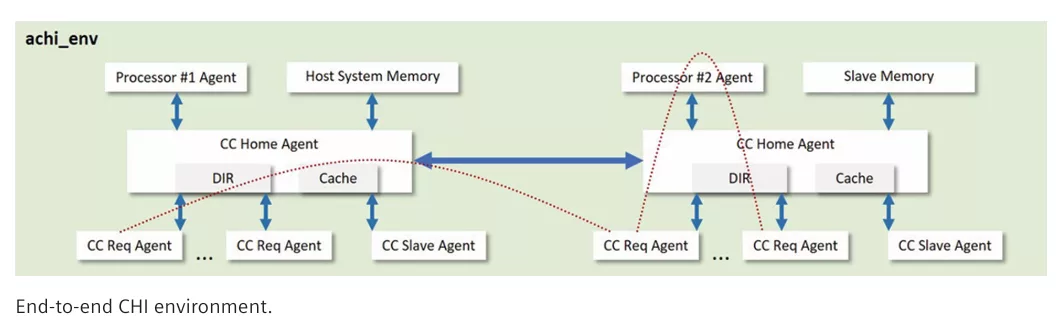

Block Diagram

Benefits

- Delivers a comprehensive, advanced UVM verification solution

- Boosts verification efficiency

- Enables development of more complex tests

- Supports more complex topologies, such as multi-path and multi-link solutions

- Increases effectiveness with core through-chip-level tests

What’s Included?

Highlights

- APB, AHB/AHB5, AXI3/AXI4/AXI4-Lite/AXI5, ACE/ACE5, CHI.Ea, CXS.B

- Master, slave, and interconnect models in active and passive mode monitors

- All models support random wait states on address, data, and response channels, including programmable response behavior using request matching

- User-defined slave read/write response queues

- Full data interleaving and multiple outstanding requests and out of order responses

- Plug and play ARM SystemVerilog assertions

- Supports ARM FastModels, allowing hybrid simulation of CPU subsystems for an overall HW/SW SoC verification process

- Includes CHI and ACE cache coherency test suites and a comprehensive set of examples

- Native SystemVerilog and UVM implementation

- ACE/CHI models N-way or fully associative cache, automatic cache management operations, and replacement strategies, including user-defined, RR, FIFO, LRU, random with backdoor, and silent automatic state transitions

- Complementary CCIX VIP also available

AMBA 5 CHI VIP

- CHI home agent interconnect with directory, request, and slave agents

- Passive monitor performs snoop response verification

- Cache state trackers and transaction-level protocol trackers improve debug

- Supports CXS.B interface for CXL/CCIX-CHI bridging, enabling unit-level verification by bypassing PCIe layers

- Cache coherency verification test suite for CXL/CCIX and CHI systems

- Protocol checking

- Performance measures

- Functional coverage

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Protocol Bridge IP core

Script/simulation approach speeds SoC verification

A comparison of Network-on-Chip and Busses

Synthesizable verification IP speeds design cycle

Synthesizable Verification IP

IP Core for an H.264 Decoder SoC

Frequently asked questions about Protocol Bridge IP cores

What is Verification IP for AMBA?

Verification IP for AMBA is a Protocol Bridge IP core from Siemens Digital Industries Software listed on Semi IP Hub.

How should engineers evaluate this Protocol Bridge?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Protocol Bridge IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.