Vendor:

MVD Cores

Category:

Video Transport

ASI Transmitter

The MVD ASI Transmitter core is a drop-in module that includes the following functions : • 188 or 204 bytes MPEG-TS input • 8B/10…

Overview

The MVD ASI Transmitter core is a drop-in module that includes the following functions :

• 188 or 204 bytes MPEG-TS input

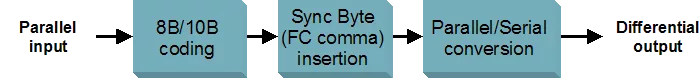

• 8B/10B Coding

• Sync Byte (FC Comma) Insertion

• Parallel/Serial Conversion

• Output signal polarity: normal or inverted

• 188 or 204 bytes MPEG-TS input

• 8B/10B Coding

• Sync Byte (FC Comma) Insertion

• Parallel/Serial Conversion

• Output signal polarity: normal or inverted

Key features

- European standard EN50083-9 Annex B

- Drop-in module for Xilinx Spartan-6, Virtex-6, Artix-7, Kintex-7, Virtex-7, Zynq FPGAs

- 135MHz Single clock

- Supports 188 or 204 bytes packet input

- Supports Data Packet or Data Burst format

- Choice of the output signal polarity

- Single channel – support for multi channel

- Full synthesizable RTL VHDL design (not delivered) for easy customization

Block Diagram

MVD_ASI_TX block diagram

Applications

- ASI Transmitter may be used in applications related to DVB/MPEG-2 transport streams.

What’s Included?

- Datasheet

- Netlist for core generation

- VHDL top file

- VHDL source code : can be delivered as an option under NDA and other specific clauses

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Part Number

MVD_ASI_TX

Vendor

MVD Cores

Provider

MVD Cores

HQ:

France

MVD Cores is an engineering team highly specialized in Digital Video Broadcasting (DVB) and FPGA technologies.

We provide IP cores for Processing, Transporting and Transmission of MPEG, DVB, ATSC & IPTV standards for Xilinx FPGAs.

The products and services catalog contains a wide range of on-the-shelf IPs to build solutions to carry MPEG-TS to RF.

Our IPs cover almost all worldwide standards of current technologies for broadcasting over Digital Terrestrial Television (DTT), Cable TV (CATV) and Satellite.

Learn more about Video Transport IP core

Introduction to Embedded DisplayPort (eDP) version 1.5

Tfox

Enabling High Performance SoCs Through Multi-Die Re-use

This paper gives a high-level overview of a technique for rapid design of new IC designs using multiple dice packaged in a variety of aggregations allowing for differnent performance levels and price points to be achieved. The technique relies on a new high-bandwidth low pin-count communication channel between two or more dice.

An HDTV SoC Based on a Mixed Circuit-Switched / NoC Interconnect Architecture (STBus/VSTNoC)

This paper presents the interconnect solution adopted for an HDTV SoC developed in HVD division of STM. The SoC is a one-chip satellite HDTV set-top box IC developed in 65nm technology. The interconnect of this HDTV SoC is the first in STM implementing a mixed architecture based on the circuit-switched interconnect named STBus and the new NoC interconnect named VSTNoC.

Steps for Delivering Multimedia Over 5 GHz WLANs

Steps for Delivering Multimedia Over 5 GHz WLANs

Tutorial: The H.264 Scalable Video Codec (SVC)

The H.264 Scalable Video Codec (SVC) reduces network bandwidth, eliminates transcoding, and simplifies storage management. Here's how it works.

Frequently asked questions about Video Transport IP cores

What is ASI Transmitter?

ASI Transmitter is a Video Transport IP core from MVD Cores listed on Semi IP Hub.

How should engineers evaluate this Video Transport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Video Transport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.