AMBA CXS Assertion IP

AMBA CXS Assertion IP provides a smart way to verify the ARM AMBA CXS component of a SOC or a ASIC.

Overview

AMBA CXS Assertion IP provides a smart way to verify the ARM AMBA CXS component of a SOC or a ASIC. The SmartDV's AMBA CXS Assertion IP is fully compliant with standard AMBA CXS Specification.

AMBA CXS Assertion IP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

AMBA CXS Assertion IP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Specification Compliance

- Compliant with the latest ARM AMBA CXS specification.

- Supports credit exchange mechanism.

- Supports Link activation and deactivation.

- Support for skipping link activation.

- Configurable credit mechanism including dynamic and pre-allocated credit control.

- Support for Interface properties and possible options as per protocol.

- Supports continuous delivery of data - uninterrupted transmission of packets.

- Fine grain control of below:

- Flit packets placement

- Packet control fields

- Ability to configure the width of all signals.

- Support for error injection during Link activation and deactivation.

- Programmable Protocol signal delays.

- Rich set of configuration parameters to control CXS functionality.

- Transaction logging and Performance Reporting support.

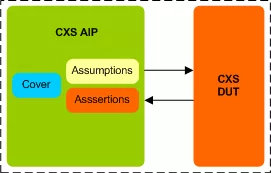

Block Diagram

Benefits

- Runs in every major formal and simulation environment.

What’s Included?

- Detailed documentation of Assertion IP usage.

- Documentation also contains User's Guide and Release notes.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Custom IP core

Breaking the Bandwidth Barrier: Enabling Celestial AI’s Photonic Fabric™ with Custom ESD IP on TSMC’s 5nm Platform

A New Era for Edge AI: Codasip’s Custom Vector Processor Drives the SYCLOPS Mission

RISC-V basics: The truth about custom extensions

Automatically Retargeting Hardware and Code Generation for RISC-V Custom Instructions

Unlock early software development for custom RISC-V designs with faster simulation

Frequently asked questions about Custom Die-to-Die IP cores

What is AMBA CXS Assertion IP?

AMBA CXS Assertion IP is a Custom IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Custom?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Custom IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.