Simulation VIP for AMBA CHI-C2C

Best-in-class Arm® AMBA® CHI-C2C Verification IP (VIP) for your IP, SoC, and System-level Design Testing Cadence provides a matur…

Overview

Best-in-class Arm® AMBA® CHI-C2C Verification IP (VIP) for your IP, SoC, and System-level Design Testing

Cadence provides a mature and comprehensive Verification IP (VIP) for the Coherent Hub Interface Chip-to-Chip (CHI-C2C) specification, which is part of the Arm AMBA family of protocols. Incorporating the latest protocol updates, the Cadence Verification IP for CHI-C2C provides a complete bus functional model (BFM), integrated automatic protocol checks, and a coverage model. Designed for easy integration in testbenches at IP, systems with multiple CPUs, accelerators, or other device chiplets, the VIP for CHI-C2C provides a highly capable compliance verification solution that supports simulation, formal analysis, and hardware acceleration platforms. Cadence provides an integrated solution for interconnect verification, which supports the verification of multi-chip symmetric multiprocessor (SMP) and multi-chip coherent accelerator attach. The VIP runs on all major simulators and supports SystemVerilog and e verification languages, along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Key features

- Support C2C driving and monitoring

- UCIe connectivity

- Format X packetization

- ReqS/ReqL DataS/DataL Resp/Resp2 WrReqDataS/WrReqDataL, Snoop and MiscU message types

- Multi-container messaging

- Credit support in MiscU/protocol-header message (no data credit pool)

- Dvm connect/link activation/system coherency initialization flows

- Property exchange

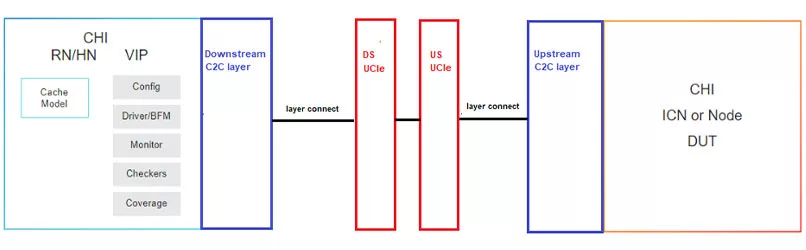

Block Diagram

Benefits

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Generates constrained-random bus traffic with predefined error injection

- Callbacks access at multiple queue points for scoreboarding and data manipulation

- Provides comprehensive checking and coverage model

- Includes embedded cache model in RN-F models

- Packet tracker for ease of debugging

- Seamless integration with System Verification Scoreboard (SVD) and System Performance Analyzer (SPA)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Custom IP core

Breaking the Bandwidth Barrier: Enabling Celestial AI’s Photonic Fabric™ with Custom ESD IP on TSMC’s 5nm Platform

A New Era for Edge AI: Codasip’s Custom Vector Processor Drives the SYCLOPS Mission

RISC-V basics: The truth about custom extensions

Automatically Retargeting Hardware and Code Generation for RISC-V Custom Instructions

Unlock early software development for custom RISC-V designs with faster simulation

Frequently asked questions about Custom Die-to-Die IP cores

What is Simulation VIP for AMBA CHI-C2C?

Simulation VIP for AMBA CHI-C2C is a Custom IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Custom?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Custom IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.