CXS a/b Verification IP

The CXS Verification IP provides an effective & efficient way to verify CXS ON Chip or OFF Chip interface.

Overview

The CXS Verification IP provides an effective & efficient way to verify CXS ON Chip or OFF Chip interface. The CXS VIP is fully compliant with standard CXS specifications Version A. This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design cycle time.

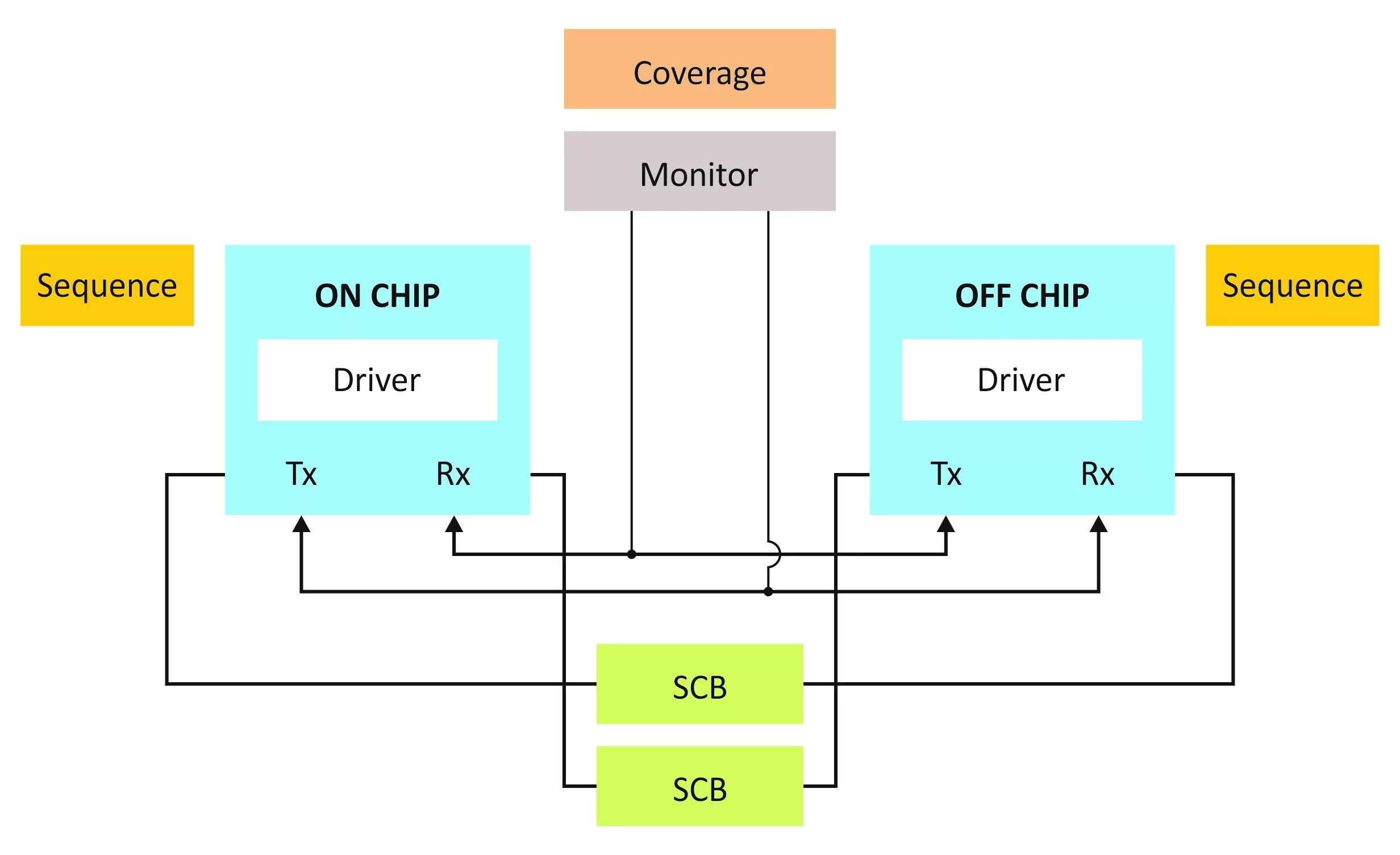

Block Diagram

Benefits

- Available in native SystemVerilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure highest levels of quality

- Availability of Compliance & Regression Test Suites

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and cover points with connectivity example for all the components

- Consistency of interface, installation, operation and documentation across all our VIPs

- Provide complete solution and easy integration in IP and SoC environment

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about Custom IP core

Breaking the Bandwidth Barrier: Enabling Celestial AI’s Photonic Fabric™ with Custom ESD IP on TSMC’s 5nm Platform

A New Era for Edge AI: Codasip’s Custom Vector Processor Drives the SYCLOPS Mission

RISC-V basics: The truth about custom extensions

Automatically Retargeting Hardware and Code Generation for RISC-V Custom Instructions

Unlock early software development for custom RISC-V designs with faster simulation

Frequently asked questions about Custom Die-to-Die IP cores

What is CXS a/b Verification IP?

CXS a/b Verification IP is a Custom IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this Custom?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Custom IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.