Die-to-Die, 112G Ultra-Extra Short Reach PHY Ported to TSMC 12FFC X16, North/South (vertical) poly orientation

The XSR PHY IP for 112Gbps per lane die-to-die connectivity enables high-bandwidth ultra and extra short reach interfaces in mult…

Overview

The XSR PHY IP for 112Gbps per lane die-to-die connectivity enables high-bandwidth ultra and extra short reach interfaces in multi-chip modules (MCMs) for hyperscale data center, AI, and networking applications. The low-latency, low-power, and compact PHY supports NRZ and PAM-4 signaling from 2.5G to 112G data rates and is compliant with the OIF CEI-112G and CEI-56G standards for extra-short reach (XSR) links. The XSR PHY offers a flexible layout for maximum bandwidth per die edge by allowing the placement of the square macros along all edges of the die. It deploys 16-lane transmit and receive macros for optimized segmentation on the multiple dies. The robust DLL-based clock-forwarded architecture enables high energy efficiency while supporting reliable links of up to 50 millimeters for large MCMs. The PHY enables multi-die connectivity over organic substrates, which helps reduce packaging costs without requiring advanced interposer-based packaging over shorter distances. The embedded bit error rate (BER) tester and nondestructive 2D eye monitor capability provide on-chip testability and visibility into channel performance. Besides the PMA and PMD, the PHY includes a raw PCS to facilitate the interface with the on-chip network, regardless of the existing networking protocol. The XSR IP is combined with the comprehensive routing feasibility analysis, package substrate guidelines, signal and power integrity models, and crosstalk analysis for fast and reliable integration into SoCs.

Key features

- 16-lane TX and RX square macros for placement in any edge of the die

- Supports 2.5G to 112G data rates, enabling very high bandwidth per mm of beachfront for die-to-die and die-to-optical engine connectivity

- Implements NRZ and PAM-4 signaling

- Meets the performance, efficiency, and reliability requirements of die-to-die interconnects

- Robust DLL-based, clock-forwarded architecture minimizes complexity and power dissipation

- Linear equalization and T-Coils in RX and TX allow compliance to XSR links up to 50mm for large MCM designs

- Low jitter phase-locked loops (PLLs) provide robust timing recovery and better jitter performance

- Compliant with the OIF CEI-112G and CEI-56G standards for XSR links

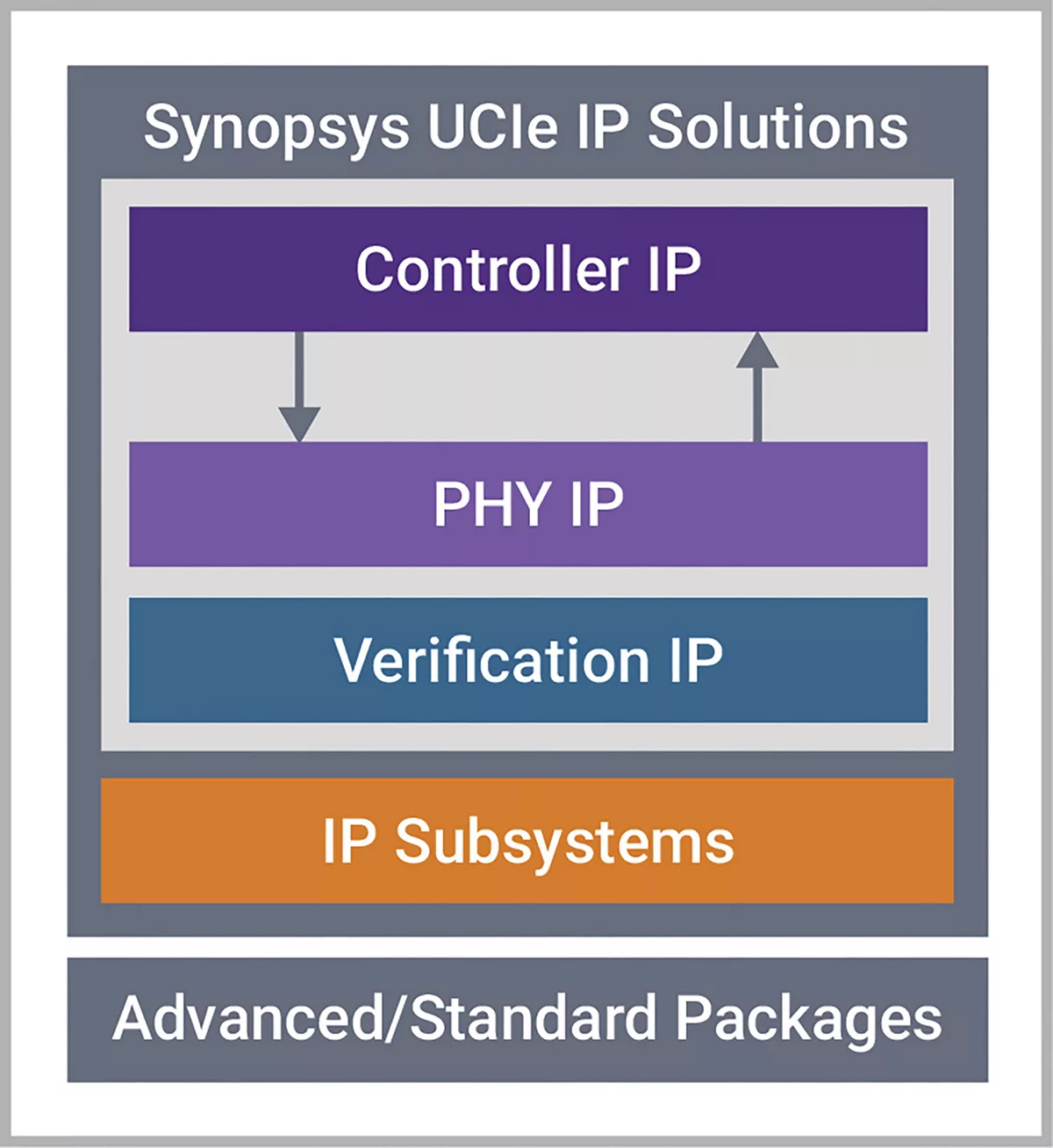

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 12nm | FFC | — |

Specifications

Identity

Provider

Learn more about Custom IP core

Breaking the Bandwidth Barrier: Enabling Celestial AI’s Photonic Fabric™ with Custom ESD IP on TSMC’s 5nm Platform

A New Era for Edge AI: Codasip’s Custom Vector Processor Drives the SYCLOPS Mission

RISC-V basics: The truth about custom extensions

Automatically Retargeting Hardware and Code Generation for RISC-V Custom Instructions

Unlock early software development for custom RISC-V designs with faster simulation

Frequently asked questions about Custom Die-to-Die IP cores

What is Die-to-Die, 112G Ultra-Extra Short Reach PHY Ported to TSMC 12FFC X16, North/South (vertical) poly orientation?

Die-to-Die, 112G Ultra-Extra Short Reach PHY Ported to TSMC 12FFC X16, North/South (vertical) poly orientation is a Custom IP core from Synopsys, Inc. listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Custom?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Custom IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.