Simulation VIP for AMBA CXS

Cadence provides a mature and comprehensive Verification IP (VIP) for the CXS specification which is part of the Arm® AMBA® famil…

Overview

Cadence provides a mature and comprehensive Verification IP (VIP) for the CXS specification which is part of the Arm® AMBA® family of protocols. Incorporating the latest protocol updates, the Cadence® VIP for CXS is designed for easy integration in testbenches at IP, system-on-chip (SoC), and system levels. The VIP helps you reduce time to test, accelerate verification closure, and ensure end-product quality. The CXS VIP runs on all major simulators and supports SystemVerilog and e verification languages along with associated methodologies, including the Universal Verification Methodology (UVM) and Open Verification Methodology (OVM).

Supported specification: AMBA CXS v2.0 and Issue B update.

Key features

- CCIX Support

- Packs and unpacks CCIX messages to interface Arm interconnects (CMN600, CMN700, others) with CCIX support and works seamlessly with CCIX PRL VIP

- Transaction Types

- Supports monitoring and driving of all transaction types

- Credit Grant

- Supports different credit grant allocation modes

- Delay Control

- Delay controls for all interface signals

- Multiple Packets in Single Flit

- Supports multiple packets in a single flit

- Data Check

- Data parity checks

- Ignore Deactivation Hint

- Supports ignoring deactivation hint

- Replication

- Supports replication mode

- Continuous Data

- Supports continuous data mode

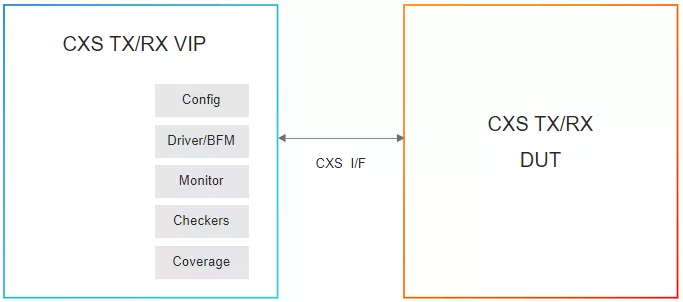

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Custom IP core

Breaking the Bandwidth Barrier: Enabling Celestial AI’s Photonic Fabric™ with Custom ESD IP on TSMC’s 5nm Platform

A New Era for Edge AI: Codasip’s Custom Vector Processor Drives the SYCLOPS Mission

RISC-V basics: The truth about custom extensions

Automatically Retargeting Hardware and Code Generation for RISC-V Custom Instructions

Unlock early software development for custom RISC-V designs with faster simulation

Frequently asked questions about Custom Die-to-Die IP cores

What is Simulation VIP for AMBA CXS?

Simulation VIP for AMBA CXS is a Custom IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Custom?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Custom IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.