Multiprotocol SerDes PMA

Our SerDes architecture is in production in processes ranging from 12nm to 180nm and at rates from 100Mbps to 32.75Gbps and prove…

Overview

Our SerDes architecture is in production in processes ranging from 12nm to 180nm and at rates from 100Mbps to 32.75Gbps and proven in 6nm. We offer targeted PHYs including JESD204, XAUI, CPRI, SGMII, CPRI, OIF-CEI, V-by-One HS, Infiniband, PCIe1/2/3/4/5 and Serial RapidIO, and a Multiprotocol PMAs covering over 30 protocols from below 250Mbps to 32.75Gbps as well as SerDes designed for custom requirements. We partner with leading controller vendors to provide a complete solution, and can provide a complete PCIe PHY including PIPE PCS.

Key features

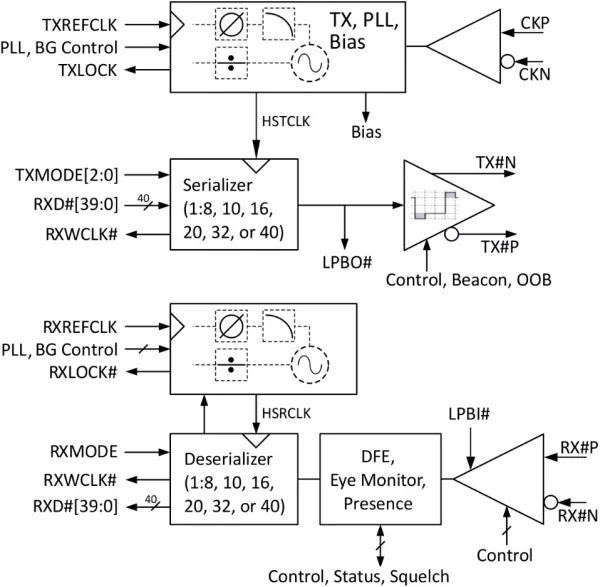

- Supports over 30 protocols including CEI 6G & 11G SR, MR, LR, Ethernet 10GBASE-X/S/K/R, PCIe Gen1/2/3/4, V-by-One HS/US, CPRI, PON, OTN/OTU, 3GSDI, JESD204A/B/C, SATA1-3, XAUI, SGMII

- Programmable (De)Serialization width: 8, 10, 16, 20, 32, or 40 bit

- Tx ring PLL includes fractional multiplication, spread spectrum and Jitter Cleaner function for Sync-E and OTU

- Core-voltage line driver with programmable pre-and post-emphasis

- Out-of-band, electrical idle signaling capability for SAS, SATA, and PCIe

- Ultra-low-Latency optimized PMAs with in-PMA latency below 13UI (<1.3ns at 10.3Gbps): See this overview.

- Burst mode CDR with tCDR < 150UI

- Programmable CTLE and adaptive 5-Tap Decision Feedback Equalizer for poor channels

- Non-destructive eye monitor to measure eye opening at data slicer on chip

Block Diagram

Applications

- Programmable devices needing to support over 30 different protocols

- AFE -- FPGA interfaces

- 10G-KR Ethernet

- SATA/SAS interfaces

- UHD-TV (4k TV) displays

- MFPs

- Scanners

- Semi-custom chip-chip interfaces

- Backplanes

What’s Included?

- GDSII

- CDL Netlist (MG Calibre Compatible)

- Functional Verilog Model

- Liberty timing models (.lib)

- LEF

- Application Note with integration and production test guidelines

- Signal Integrity simulations using customer package models

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 40nm | LP | — |

Specifications

Identity

Provider

Learn more about Multi-Protocol PHY IP core

How a 16Gbps Multi-link, Multi-protocol SerDes PHY Can Transform Datacenter Connectivity

16Gbps SerDes Multiprotocol Multilink PHY IP

32G Multi-Protocol SerDes PHY Out the Gate

New 16Gbps Multi-link, Multi-protocol SerDes PHY Enhances Datacenter Connectivity

One PHY, Zero Tradeoffs: Multi-Protocol PHY for Edge AI Interface Consolidation

Frequently asked questions about Multi-Protocol PHY IP cores

What is Multiprotocol SerDes PMA?

Multiprotocol SerDes PMA is a Multi-Protocol PHY IP core from Silicon Creations listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this Multi-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Multi-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.