1 Gbps Rail to Rail LVDS receiver

065TSMC_LVDS_08 is LVDS receiver with rail to rail input range.

Overview

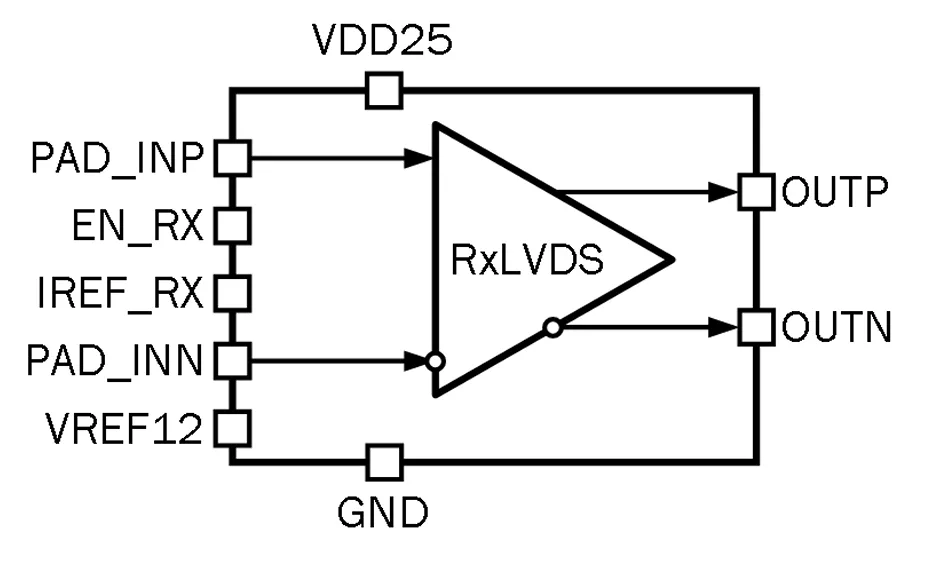

065TSMC_LVDS_08 is LVDS receiver with rail to rail input range. The interface to the core logic includes the output signal pins (OUTP, OUTN) to receive data and the control pin EN_RX to configure the state of the receiver. The VREF12 pin is input voltage reference. Pin IREF_RX to get current reference from receiver bias. PAD_INP and PAD_INN are complementary input to connect to the bonding pads. This LVDS receiver does not employ hysteresis, and therefore does not comply with the hysteresis requirement of the TIA and IEEE standards for LVDS differential signaling at the specified rates.

Key features

- TSMC CMOS 0.065 um

- 2.5 V analog power supply

- 1.2 V digital power supply

- 1.2 V CMOS input and output logic signals

- 1 Gbps (DDR MODE) switching rates

- Conforms to TIA/EIA-644 LVDS standards without hysteresis

- Rail to rail input range

- Temperature range: -40 °C to + 125 °C

- Optimized for pad-limited layout design

- Portable to other technologies (upon request)

Block Diagram

Applications

- Point-to-point data receiver

- Multidrop buses

- Clock distribution

- Backplane receiver

- Backplane data receiver

- Cable data receiver

What’s Included?

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentation

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 65nm | GP | Silicon Proven |

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is 1 Gbps Rail to Rail LVDS receiver?

1 Gbps Rail to Rail LVDS receiver is a Single-Protocol PHY IP core from NTLab listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.