LVDS 160MHz 8-Lane PHY TX IP on TSMC 16FFC

The CL12491M8TIP160 transmitter converts parallel RGB data and 4bits of HYNC,VSYNC,DE and Control) of CMOS parallel data into ser…

Overview

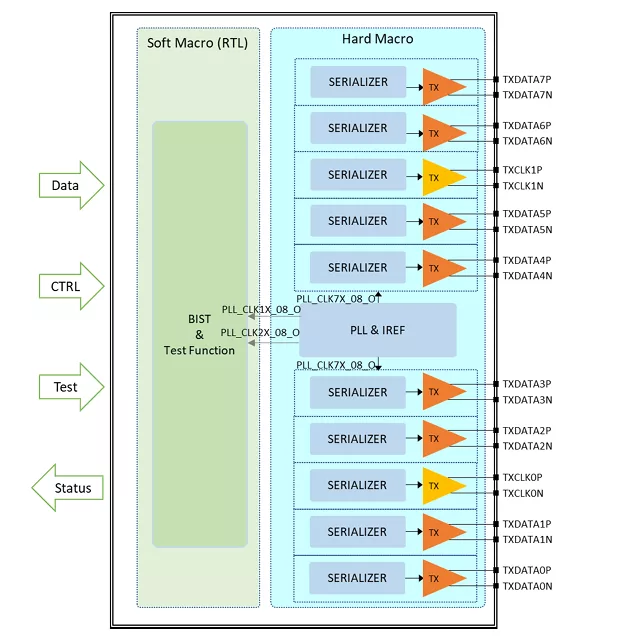

The CL12491M8TIP160 transmitter converts parallel RGB data and 4bits of HYNC,VSYNC,DE and Control) of CMOS parallel data into serial LVDS data streams. A phase-locked clock is transmitted in parallel with the data streams over a dedicated LVDS link. The polarity of differential signals for each data lane can be controlled. The transmit clock frequency of 160MHz, 24bits RGB data, and 4bits LCD timing & control data (HSYNC, VSYNC, DE,Control1) are transmitted at the rate of 1.12Gbps per LVDS data lane. The CL12491M8TIP160 transmitter is an ideal means to solve EMI and cable size issues associated with high-speed CMOS interface.

The CL12491M8TIP160 has integrated PLL with spread spectrum clock option. The targeted SSC modulating frequency is designed to be in the range of 10KHz ~ 30KHz, with modulation depth up to 3.1%, centered spread.

* This IP can also be optimized for single-link use.

* Porting is also possible for processes other than the target process.

Key features

- Data Rate: Up to 1.12Gbps

- Clock polarity programmable

- Data polarity for each data lane is programmable

- Integrated PLL with spread Spectrum option

- 4 programable level of output differential voltage

- RX detection circuit to detect connectivity to device

- Clock-in-fail detection to detect malfunction of clock source

- BIST function for loopback test

- LVDS Operational modes supported:

- to support 1080p@60fps with single link (4 data lanes + 1 clock lane)

- to support 2560x1440 @60fps with dual link (8 data lanes + 1 or 2 clock lane)

Block Diagram

Benefits

- By implimenting the CL12491M8TIP160 in an SOC, it easily realizes the function of converting parallel RGB data and 4-bit CMOS parallel data to LVDS data stream. It can support displays with resolutions of FHD (single link) and WQHD (dual link). The built-in PLL with spread spectrum clock option makes it easy to reduce EMI in the set.

- Process porting is available according to customer requests.

- This IP can be implemented in a lane units and can be tailored to meet customer specifications.

Applications

- Display Application

- Automotive

- Navigation system

- DSC(Digital Still Camera)

What’s Included?

- Verilog Model (verilog / vcs)

- .db file / .lib(Option) file

- symbol / LVS netlist / Hspice netlist(Option)

- LEF, layer map file, layout technology file

- Layout Verification Report (DRC & LVS), Command file

- Datasheet

- Packaging and Layout Guideline / PCB Guideline

- Static Delay Analysis (STA) Guideline

- Testing Guideline (Option)

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 16nm | FFC | Silicon Proven |

Specifications

Identity

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is LVDS 160MHz 8-Lane PHY TX IP on TSMC 16FFC?

LVDS 160MHz 8-Lane PHY TX IP on TSMC 16FFC is a Single-Protocol PHY IP core from Curious Corp. listed on Semi IP Hub. It is listed with support for tsmc Silicon Proven.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.