Synopsys Targets 400G Hyperscale Data Centers with High-Performance Ethernet IP

DesignWare 56G Ethernet PHY Addresses the Reach and Performance Requirements of Next-Generation Leaf-Spine Network Architectures

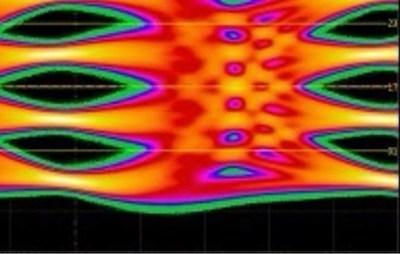

MOUNTAIN VIEW, Calif., July 24, 2018 -- Synopsys, Inc. (Nasdaq: SNPS) today announced the new DesignWare® 56G Ethernet PHY IP for emerging 400 gigabit-per-second (Gbps) hyperscale data center system-on-chips (SoCs). The advanced 56G Ethernet PHY architecture incorporates Synopsys' silicon-proven data converters with a configurable transmitter and digital signal processor (DSP)-based receiver to deliver the best power and performance tradeoffs for the target application. To meet the bandwidth needs of leaf-spine architectures, the PHY supports single and aggregated link rates from 10G to 400G Ethernet, while meeting the PAM-4 and NRZ signaling. In addition, the PHY exceeds the performance requirements of OIF and IEEE standards for chip-to-chip, backplane, and copper/optical cable interfaces. The combination of Synopsys' 56G Ethernet PHY, digital controllers, verification IP, and source code test suites gives designers a complete Ethernet IP solution for their networking data center systems.

For a more robust timing recovery and better jitter performance, the 56G Ethernet PHY receiver features a multi-loop clock and data recovery circuit, as well as a full-featured DSP. The unique architecture of the PAM-4 transmitter allows for precise feed forward equalization to achieve channel performance requirements. The 56G Ethernet PHY's scalable architecture provides a foundation for next-generation 800G Ethernet applications requiring 112G connectivity.

"The growing amount of bandwidth required in the data center is increasing the workload demand on the network infrastructure," said John Koeter, vice president of marketing for IP at Synopsys. "Synopsys' DesignWare 56G Ethernet IP allows designers to meet the high-performance Ethernet connectivity requirements of 400G hyperscale data center SoCs with less risk."

Availability & Additional Resources

The silicon design kit for the DesignWare 56G Ethernet PHY in 16-nm and 7-nm FinFET processes are scheduled to be available in Q3 of 2018 and Q4 of 2018, respectively.

For more information, visit the DesignWare 56G Ethernet PHY IP, DesignWare Ethernet IP Solutions, and VC Verification IP for Ethernet web pages.

About DesignWare IP

Synopsys is a leading provider of high-quality, silicon-proven IP solutions for SoC designs. The broad DesignWare IP portfolio includes logic libraries, embedded memories, embedded test, analog IP, wired and wireless interface IP, security IP, embedded processors, and subsystems. To accelerate prototyping, software development and integration of IP into SoCs, Synopsys' IP Accelerated initiative offers IP prototyping kits, IP software development kits, and IP subsystems. Synopsys' extensive investment in IP quality, comprehensive technical support, and robust IP development methodology enable designers to reduce integration risk and accelerate time-to-market. For more information on DesignWare IP, visit https://www.synopsys.com/designware.

About Synopsys

Synopsys, Inc. (Nasdaq: SNPS) is the Silicon to Software™ partner for innovative companies developing the electronic products and software applications we rely on every day. As the world's 15th largest software company, Synopsys has a long history of being a global leader in electronic design automation (EDA) and semiconductor IP and is also growing its leadership in software security and quality solutions. Whether you're a system-on-chip (SoC) designer creating advanced semiconductors, or a software developer writing applications that require the highest security and quality, Synopsys has the solutions needed to deliver innovative, high-quality, secure products. Learn more at www.synopsys.com.

Related Semiconductor IP

Related News

- TeraSignal Demonstrates Interoperability with Synopsys 112G Ethernet PHY IP for High-Speed Linear Optics Connectivity

- Inomize Selects Synopsys' Silicon-Proven 56G Ethernet PHY IP for High-Performance Computing and Communications SoC Design

- Chelsio Adopts Synopsys DesignWare 56G Ethernet PHY IP to Accelerate Development of High-Performance Computing SoC

- 1G Ethernet PHY IP Cores solution for all your Gigabit network applications is available for immediate licensing

Latest News

- TSMC Chases Soaring AI Demand

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing