Rambus Expands Portfolio of DDR5 Memory Interface Chips for Data Centers and PCs

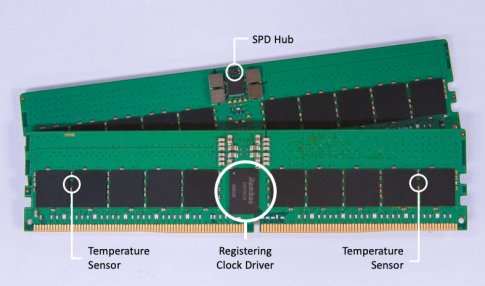

SAN JOSE, Calif. – July 18, 2022 – Rambus Inc. (NASDAQ: RMBS), a premier chip and silicon IP provider making data faster and safer, today announced the expansion of its DDR5 memory interface chip portfolio with the addition of the Rambus SPD (Serial Presence Detect) Hub and Temperature Sensor, complementing the industry-leading Rambus Registering Clock Driver (RCD). DDR5 achieves greater memory bandwidth and capacity by employing a new module architecture with an expanded chipset. The SPD Hub and Temperature Sensors improve DDR5 Dual Inline Memory Module (DIMM) system management and thermal control to deliver higher performance within the desired power envelope for servers, desktops and laptops.

“The new performance levels of DDR5 memory place an increased premium on signal integrity and thermal management for server and client DIMMs,” said Sean Fan, chief operating officer at Rambus. “With over 30 years of memory subsystem design experience, Rambus is ideally positioned to deliver DDR5 chipset solutions which enable breakthrough bandwidth and capacity for advanced computing systems.”

“The strong collaboration between Intel and SPD ecosystem partners like Rambus, delivers critical chip solutions for Intel’s next generation DDR5-based systems, scaling server, desktop and laptop performance to new levels,” said Dr. Dimitrios Ziakas, VP of Memory and IO Technologies at Intel. “Our joint efforts to advance DDR5-based computing systems is setting the stage for Intel’s DDR5 advance over multiple generations and the next level of performance for data centers and consumers.”

“DDR5 provides a significant increase in performance for computing systems,” said Shane Rau, research vice president, Computing Semiconductors at IDC. “However, DDR5 memory modules require new components to function, components like SPD hubs and temperature sensors are important components for client and server systems.”

Part of the Rambus server and client DDR5 memory interface chipsets, the SPD Hub and Temperature Sensor combine with the RCD to deliver high-performance, high-capacity memory solutions for DDR5 computing systems. Both the SPD Hub and Temperature Sensor are critical components on a memory module that sense and report important data for system configuration and thermal management. The SPD Hub is used in both server and client modules, including RDIMMs, UDIMMS and SODIMMS, and the temperature sensor is designed for server RDIMMs.

Key features of the SPD Hub (SPD5118) include:

- I2C and I3C bus serial interface support

- Advanced reliability features

- Expanded NVM space for customer-specific applications

- Low latency for fastest I3C bus rates

- Integrated temperature sensor

- Meets or exceeds all JEDEC DDR5 SPD Hub operational requirements (JESD300-5A)

Key features of the Temperature Sensor (TS5110) include:

- Precision thermal sensing

- I2C and I3C bus serial interface support

- Low latency for fastest I3C bus rates

- Meets or exceeds all JEDEC DDR5 Temperature Sensor operational requirements (JESD302-1.01)

Rambus Expands Portfolio of DDR5 Memory Interface Chips for Data Centers and PCs

Availability and Additional Information

The Rambus SPD Hub and Temperature Sensor are both available today. For additional information, please visit https://www.rambus.com/ddr5-dimm-chipset.

Related Semiconductor IP

- DDR5 MRDIMM PHY and Controller

- DDR5 & DDR4 COMBO IO for memory controller PHY, 4800Mbps on TSMC 12nm

- DDR5 LRRDIMM Verification IP

- DDR5 RDIMM Verification IP

- MRDIMM DDR5 & DDR5/4 PHY & Controller

Related News

- Rambus Expands Industry-Leading Memory Interface Chip Offering to High-Performance PCs with DDR5 Client Clock Driver

- Rambus Expands Chipset for Advanced Data Center Memory Modules with DDR5 Server PMICs

- Rambus Delivers 6400 MT/s DDR5 Registering Clock Driver to Advance Server Memory Performance

- Rambus Advances Data Center Server Performance with Industry-First Gen4 DDR5 RCD

Latest News

- EU DARE Project Is Scrambling to Replace Codasip

- Sofics and Alcyon Photonics Partner to Support Next-Generation Photonic Systems

- QuickLogic Appoints Quantum Leap Solutions as Authorized Sales Representative

- Cadence and NVIDIA Expand Partnership to Reinvent Engineering for the Age of AI and Accelerated Computing

- Cadence and Google Collaborate to Scale AI-Driven Chip Design with ChipStack AI Super Agent on Google Cloud