Fibre Channel 8G, 4G, 2G IP

Welcome to the ultimate Fibre Channel 8G, 4G, 2G IP hub! Explore our vast directory of Fibre Channel 8G, 4G, 2G IP

All offers in

Fibre Channel 8G, 4G, 2G IP

Filter

Compare

11

Fibre Channel 8G, 4G, 2G IP

from

3

vendors

(1

-

10)

-

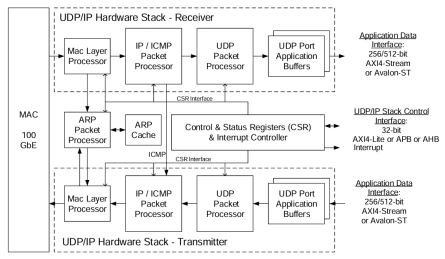

UDP/IP – 100 GbE Protocol Hardware Stack

- 100 GbE network links

- Low latency, high-performance wire-line performance

- Internet Protocol (IP) Packet Processor: IP & ICMP (Internet Control Message Protocol) Protocol; Host IP address filter, IP header checksum check & generator, userselectable Maximum Transmission Unit (MTU), Unicast & MulticastPacket support; Compliance with IETF IPv4/IPv6 RFCs

- User Datagram Protocol (UDP) Packet Processor: Support for up to 256 UDP Ports; UDP header checksum check & generator; Compliance with IETF UDP RFCs

-

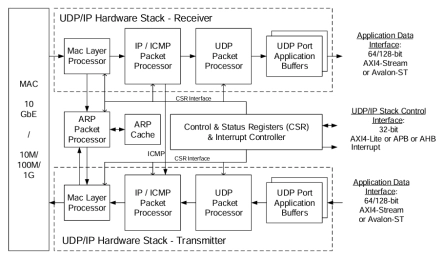

UDP/IP – 10 GbE Protocol Hardware Stack

- 10 GbE network links

- Low latency, high-performance wire-line performance

- Internet Protocol (IP) Packet Processor:

- User Datagram Protocol (UDP) Packet Processor:

-

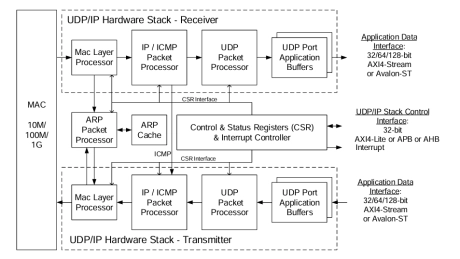

UDP/IP – 1 GbE Protocol Hardware Stack

- 1 GbE network links, including 100/100 MbE (triple play)

- Low latency, high-performance wire-line performance

- Internet Protocol (IP) Packet Processor: IP & ICMP (Internet Control Message Protocol) Protocol; Host IP address filter, IP header checksum check & generator, userselectable Maximum Transmission Unit (MTU), Unicast & MulticastPacket support; Compliance with IETF IPv4/IPv6 RFCs

- User Datagram Protocol (UDP) Packet Processor: Support for up to 256 UDP Ports; UDP header checksum check & generator; Compliance with IETF UDP RFCs

-

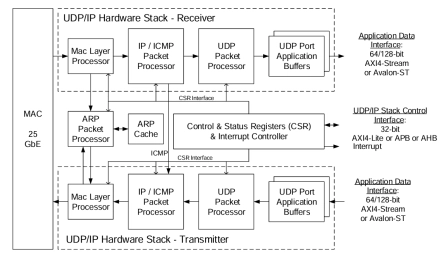

UDP/IP – 25 GbE Protocol Hardware Stack

- 25 GbE network links

- Low latency, high-performance wire-line performance

- Internet Protocol (IP) Packet Processor: IP & ICMP (Internet Control Message Protocol) Protocol; Host IP address filter, IP header checksum check & generator, userselectable Maximum Transmission Unit (MTU), Unicast & MulticastPacket support; Compliance with IETF IPv4/IPv6 RFCs

- User Datagram Protocol (UDP) Packet Processor: Support for up to 256 UDP Ports; UDP header checksum check & generator; Compliance with IETF UDP RFCs

-

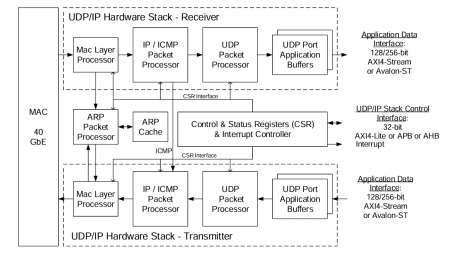

UDP/IP – 40 GbE Protocol Hardware Stack

- 40 GbE network links, including 10 GbE

- Low latency, high-performance wire-line performance

- Internet Protocol (IP) Packet Processor: IP & ICMP (Internet Control Message Protocol) Protocol; Host IP address filter, IP header checksum check & generator, userselectable Maximum Transmission Unit (MTU), Unicast & MulticastPacket support; Compliance with IETF IPv4/IPv6 RFCs

- User Datagram Protocol (UDP) Packet Processor: Support for up to 256 UDP Ports; UDP header checksum check & generator; Compliance with IETF UDP RFCs

-

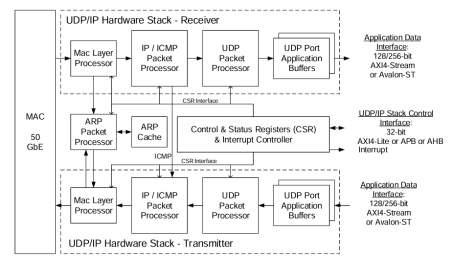

UDP/IP – 50 GbE Protocol Hardware Stack

- 50 GbE network links

- Low latency, high-performance wire-line performance

- Internet Protocol (IP) Packet Processor: IP & ICMP (Internet Control Message Protocol) Protocol; Host IP address filter, IP header checksum check & generator, userselectable Maximum Transmission Unit (MTU), Unicast & MulticastPacket support; Compliance with IETF IPv4/IPv6 RFCs

- User Datagram Protocol (UDP) Packet Processor: Support for up to 256 UDP Ports; UDP header checksum check & generator; Compliance with IETF UDP RFCs

-

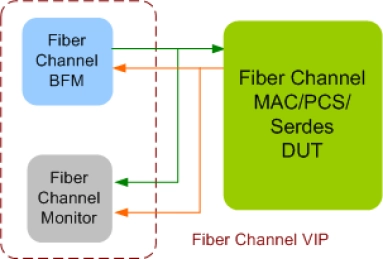

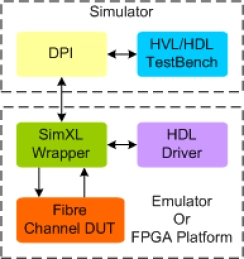

Fibre Channel Verification IP

- Compliant with the Fibre Channel framing and signaling specification FC-FS-6, Rev 0.1.

- Compliant with the Fibre Channel link service specification FC-LS-4, Rev 4.03.

- Compliant with the Fibre Channel physical interface specification FC-PI-7, Rev 0.13.

- Compliant with the Fibre Channel protocol for SCSI specification FCP-4.

-

Fibre Channel Synthesizable Transactor

- Compliant with the Fibre Channel framing and signaling specification FC-FS-6, Rev 0.1.

- Compliant with the Fibre Channel link service specification FC-LS-4, Rev 4.03.

- Compliant with the Fibre Channel physical interface specification FC-PI-7, Rev 0.13.

- Compliant with the Fibre Channel protocol for SCSI specification FCP-4.

-

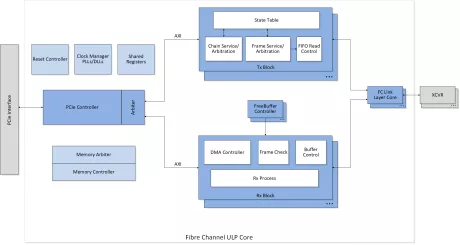

FC Upper Layer Protocol (ULP) IP Core

- FC-AE-RDMA & FC-AV compliant interface with hardware-based offload

- Hardware DMA engines map sequence data to host memory buffers

-

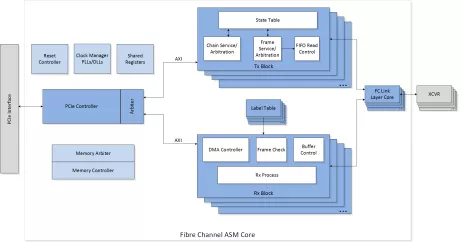

Fibre Channel ASM (Anonymous Subscriber Messaging) Core

- Message label validation checks performed in hardware

- Multiple user modes for receiving messages, including strictly mapped message-to-buffer and free-buffer implementations

- Transmit message chaining options provided

- Complete set of registers for managing core and configuring core options