Overview

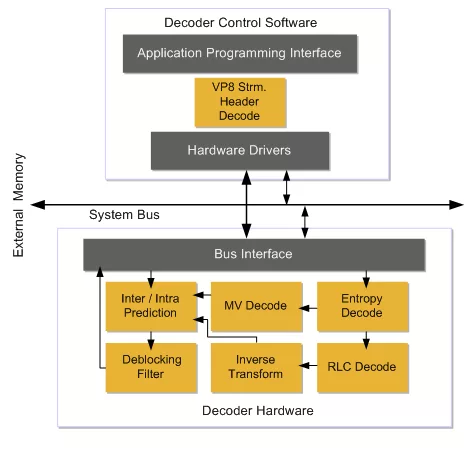

The WebM VP8 (G1) hardware decoder brings an unprecedented level of performance to enable all kinds of WebM video applications. It is the first hardware decoder in the market to encompass full WebM video support, significantly extending the video playback time of Internet-connected and HTML5-enabled battery operated devices.

Intended for chipsets targeting multimedia devices (Smart DTVs, HD set-top boxes, smart phones, tablets, Chromebooks, etc.), the WebM VP8 G1 Decoder is built on silicon-proven designs deployed in millions of chips worldwide, and provides semiconductor manufacturers with a minimal risk solution for integrating high performance video capability to their chipsets.

The video decoder design is exceptionally fast, requiring less than 100MHz clock frequency to decode 1080p video at 30 fps, and can even achieve 60fps decode for 2160p VP8 video through multi-core implementation. The core supports unlimited VP8 multi-channel decoding, enabling simultaneous playback of up to ten SD streams. It uses unique pre-fetching and buffering mechanisms to enable smooth operation with low-end SDRAMs, realizing significant savings in power and overall chip design and manufacturing costs.

the G-Series 1 is highly power efficient, consuming less than 50 milliwatts for HD video decoding, and less than 10 milliwatts for SD video.

Learn more about Video Processing IP core

This paper describes an FPGA-based high-definition video processing platform. The platform supports a wide range of applications including flat-panel TV, projection TV and video monitor.

Configurable Processors for Video Processing SOCs

Programmable FPGA devices are the perfect choice for interfacing with multiple high-resolution image sensors simultaneously...

A look at the design of multiprocessor systems-on-chips (MPSoCs) for video applications and how to optimize them for computational power and real-time performance as well as flexibility. Part 1: Architectural approaches to video processing

Building a high-performance, quad-channel H.264 encoder using low-cost, low-power FPGA architecture.

Adding to its growing portfolio of licensable silicon IP subsystems, ARC has announced five configurable video processing subsystems. The subsystems range from the smallest-size AV 402V to the highest-performance AV 417V, and support multi-standard video encoding and decoding at resolutions ranging from CIF to D1.