Verification IP for I3C/I2C

The proliferation of sensors in mobile wireless and mobile-influenced products has created significant design challenges.

Overview

The proliferation of sensors in mobile wireless and mobile-influenced products has created significant design challenges. The MIPI I3C/SMBus interface has been developed to ease sensor system design architectures in mobile wireless products by providing a fast, low cost, low power, two-wire digital interface for sensors.

MIPI I3C Verification IP (VIP) supports the MIPI I3C sensor interface specification used for smartphones, wearables, IoT devices, and automotive camera systems based on MIPI CSI-2.

I3C/I2C models support the host controller interface (HCI)—a host software and host bus adaptor for communicating with the I3C controllers over local bus architectures like AHB.

I3C-Xactor works in conjunction with AMBA AHB models to comprise a complete system-level environment. MIPI CSI-2 uses I3C for the CCI interface.

Key features

- Support for I3C Basic and Full specifications and I3C Host Controller Interface (HCI)

- Support for I3C Debug and JESD 403-1 SidebandBus

- Support for I2C and SMBus 3.0

- Dual mode VIP models supporting master and slave

- Comprehensive directed and constrained random compliance testsuite achieves high protocol coverage for master and slave

- Comprehensive protocol checking

- Configurable reference testbench to plug in any DUT with I3C and I2C devices

- Native SystemVerilog/UVM implementation

- Open and unencrypted timing class models all timing parameters (randomize, modifiable)

- Support for I3C/I2C/SMBus command class models, all types

- Callback support for error detection and injection

- SV constraint set on all transaction classes generates rich set of normal and error packets

- Master randomly configures slaves

- Comprehensive protocol and timing checks track compliance checklist coverage and isolate DUT bugs faster

- Tracker log monitors all levels and improves debug

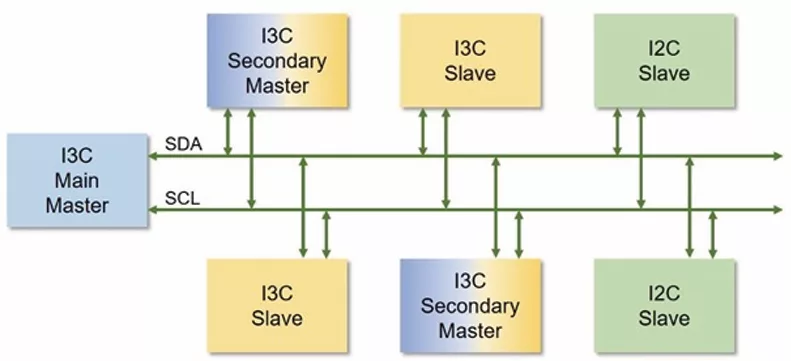

Block Diagram

Benefits

- Supports I3C/I2C/SMBus

- Includes complete models, timing, and protocol checkers

- Delivers the full range of DUT configurations

- Provides constrained random stimulus

- Offers a flexible and open architecture

- Supports native SV/UVM implementation

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about I2C / I3C IP core

Maximizing the Usability of Your Chip Development: Design with Flexibility for the Future

MIPI I3C v1.1 - A Conversation with Ken Foust

How to Connect Sensors with I3C

MIPI CCI over I3C: Faster Camera Control for SoC Architects

Arasan I3C PHY - Ternary vs. Non-Ternary

Frequently asked questions about I2C / I3C IP cores

What is Verification IP for I3C/I2C?

Verification IP for I3C/I2C is a I2C / I3C IP core from Siemens Digital Industries Software listed on Semi IP Hub.

How should engineers evaluate this I2C / I3C?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this I2C / I3C IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.