UALink PCS IP Core

Silicon agnostic and fully compliant Physical Coding Sublayer (PCS) implementation of UALink_200 specification The UA Link PCS IP…

Overview

Silicon agnostic and fully compliant Physical Coding Sublayer (PCS) implementation of UALink_200 specification

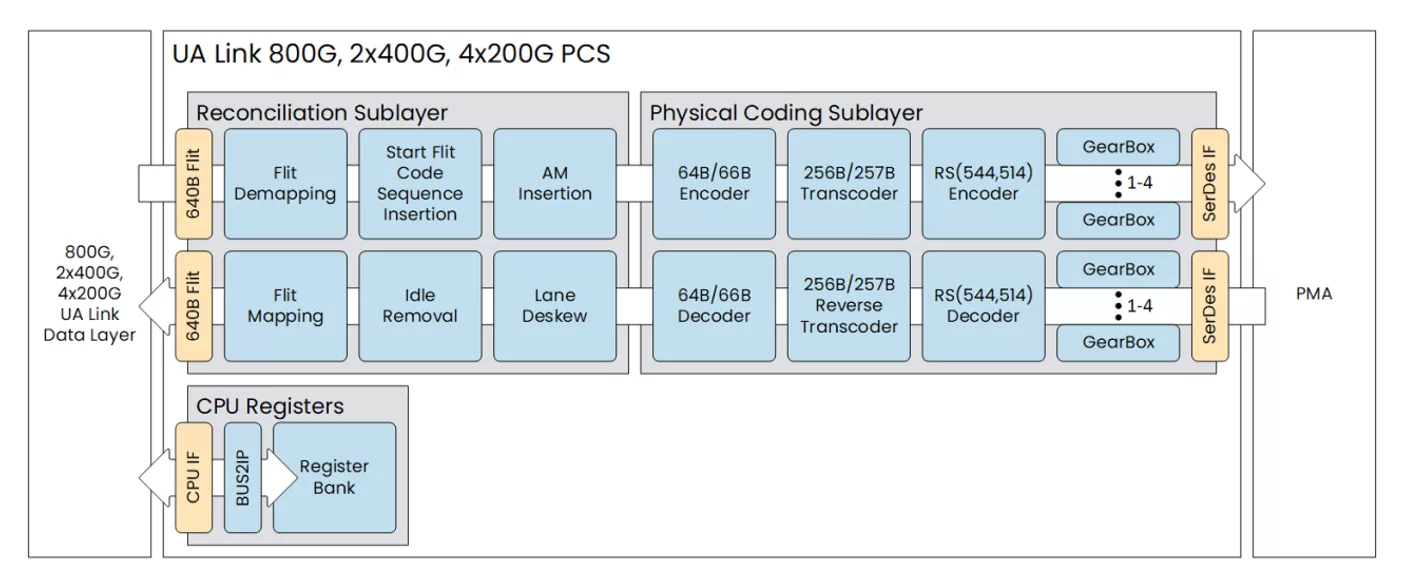

The UA Link PCS IP Core is a high-performance, silicon-agnostic and fully compliant Physical Coding Sublayer (PCS) implementation of UALink_200 specification. Designed for seamless integration into accelerator, switch, and SoC designs, it delivers deterministic low-latency, robust error correction, and compatibility with multiple high-speed Ethernet-derived link rates.

This IP core bridges the UALink Data Link Layer (DL) to the Physical Medium Attachment (PMA), ensuring optimized flit-to-codeword mapping, forward error correction (FEC), and alignment marker handling as defined in UALink_200 Standard. It is ideal for systems requiring 200–800 Gbps per Link/Station with industry-leading signal integrity and interoperability.

Key features

- UALink_200 Specification Compliant: Implements PCS functions per Rev 1.0

- Multi-Rate Support :

- 100 GBASE-KR1/CR1, 200 GBASE-KR2/CR2, 400 GBASE-KR4/CR4,

- 200 GBASE-KR1/CR1, 400 GBASE-KR2/CR2, 800 GBASE-KR4/CR4

- Low-Latency FEC 1-way & 2-way interleave options for reduced latency

- Deterministic Flit Alignment: 640B DL Flit to 680B codeword mapping

- Standards-Compatible: IEEE 802.3dj PCS & FEC compliant with UALink extensions

- Integrated Lane Alignment: Lane marker insertion/removal per UALink-defined rules

- Targeting both ASICs and FPGAs

Block Diagram

Benefits

- Test Environment: UA Link PCS IP is Tested against a VIP model in UVM regression for full functional coverage

- Silicon Agnostic: Designed in Verilog and targeting both ASICs and FPGAs

- PHY Integration: PHY Integration support with additional hours or off the shelf PHY integration package for quick and efficient deployment

- Active Support: All support is actively provided by engineers directly

What’s Included?

The IP Core can be delivered in Source code or Encrypted format.

The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual, Release Note and Quick Start Guide.

- Simulation Environment, including Simple Testbed, Test case, Test Script.

- Timing Constraints in Synopsys SDC format.

- Access to support system and direct support from Chip Interfaces Engineers.

- Test Report , Synopsys SGDC Files and Synopsys Lint, CDC and Waivers available on request

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UALink IP core

Securing UALink: Introducing Synopsys UALinkSec_200 Security Module

Validating UPLI Protocol Across Topologies with Cadence UALink VIP

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

UALink: Powering the Future of AI Compute

Frequently asked questions about UALink IP cores

What is UALink PCS IP Core?

UALink PCS IP Core is a UALink IP core from Chip Interfaces ApS listed on Semi IP Hub.

How should engineers evaluate this UALink?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UALink IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.