224G SerDes PHY and controller for UALink for AI systems

Efficient Scaling of AI Accelerators for Achieving High Performance and Throughput UALink, the standard for AI accelerator interc…

Overview

Efficient Scaling of AI Accelerators for Achieving High Performance and Throughput

UALink, the standard for AI accelerator interconnects, facilitates this scalability by providing low-latency, high-bandwidth communication. As a member of the UALink Consortium, Cadence offers verified UALink IP subsystems, including controllers and silicon-proven PHYs, optimized for robust performance in both short and long-reach applications and delivering industry-leading power, performance, and area (PPA).

Key features

Unmatched Bandwidth, Ultra-Low Latency, and Power Efficiency for AI Accelerators

- XPU-to-XPU Scale-Up Connectivity — The UALink subsystem IP enables scale-up connectivity for AI systems, supporting the emerging 1.6T and 800G networks

- Integrated Debugging Features — Includes features like Flit-play for debugging or error injection and Flit-capture for field debugging

- Multi-Line Rate Support — Supports 100G and 200G data rates

- FEC Interleave Options — 1-way, 2-way, and 4-way interleaves

- Optional Features — Packet compression, encryption, and security

- Standard Features — Atomic support, multiple VCs, bifurcation, UART buffers, DL layer loopback, DL-FLIT play and capture, transmitter pacing, MSG service, programmable RX credit, authentication tags, latency monitoring, and more

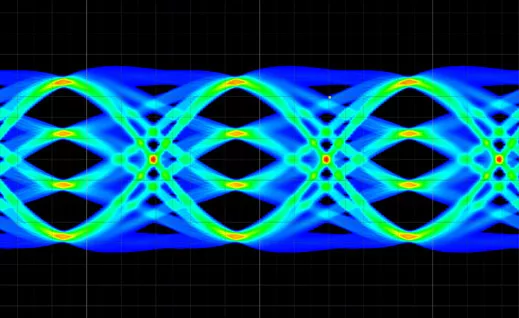

Block Diagram

Benefits

- Power-Efficient Design: Optimized for UALink

- Low-Latency: For maximum design performance

- Proven Solution: Full protocol stack implemented and verified in test chips

- Long-Reach Capability: Robust 224G 47+dB LR performance with LR/MR/VSR support at reduced power

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UALink IP core

Validating UPLI Protocol Across Topologies with Cadence UALink VIP

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

UALink: Powering the Future of AI Compute

How Ultra Ethernet And UALink Enable High-Performance, Scalable AI Networks

Frequently asked questions about UALink IP cores

What is 224G SerDes PHY and controller for UALink for AI systems?

224G SerDes PHY and controller for UALink for AI systems is a UALink IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this UALink?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UALink IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.