UALink Controller

Efficient scaling of AI accelerators is necessary for achieving breakthrough performance and throughput in modern compute environ…

Overview

Efficient scaling of AI accelerators is necessary for achieving breakthrough performance and throughput in modern compute environments. The UALink Controller, part of Cadence’s verified UALink IP subsystem, delivers ultra-low latency and high-bandwidth interconnects that enable seamless scale-up connectivity between AI accelerators. It supports memory semantics for read, write, and atomic operations, ensuring fast, coherent data handling across workloads. UALink IP provides a scalable, future-ready solution for next-generation AI infrastructure.

As a contributor member of the UALink Consortium, Cadence offers a complete UALink solution—including controller, PHY, drivers, and verification IP—optimized for both short- and long-reach applications.

Key features

- Multi-Line Rate Support: Compatible with 100G and 200G data rates (per lane).

- FEC Interleave Options: 1-way, 2-way, and 4-way interleave modes for latency optimization.

- Integrated Debugging Tools: Includes flit-play for error injection and flit-capture for field diagnostics.

- Security Enhancements: Optional secure layer integration for authentication and encryption.

- Protocol Flexibility: Supports all 1.0 features.

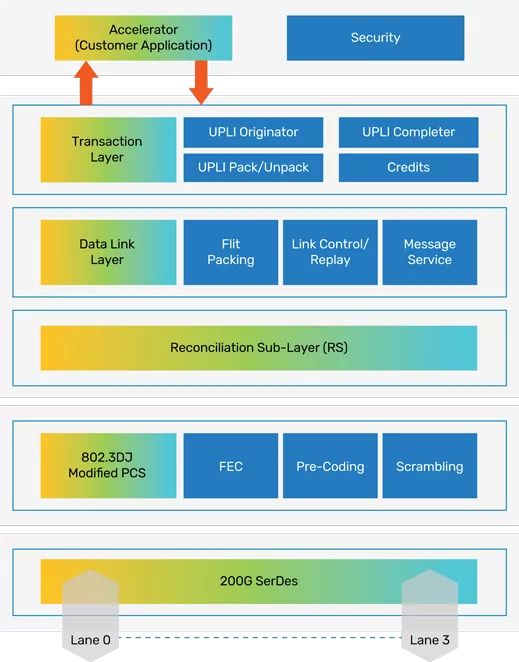

Block Diagram

Benefits

- Power-Efficient Design: Engineered for optimal performance-per-watt across AI workloads.

- Low-Latency Architecture: Minimizes communication delays for real-time responsiveness.

- Scalability: Optimized PHY, PCS, and controller for scale-up connectivity.

- Proven Solution: Fully verified protocol stack with controller and PHY integration.

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UALink IP core

Validating UPLI Protocol Across Topologies with Cadence UALink VIP

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

UALink: Powering the Future of AI Compute

How Ultra Ethernet And UALink Enable High-Performance, Scalable AI Networks

Frequently asked questions about UALink IP cores

What is UALink Controller?

UALink Controller is a UALink IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this UALink?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UALink IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.