Securing UALink: Introducing Synopsys UALinkSec_200 Security Module

Secure high-speed data with Synopsys UALinkSec_200 - confidentiality, integrity, and performance for scalable AI data center infrastructures.

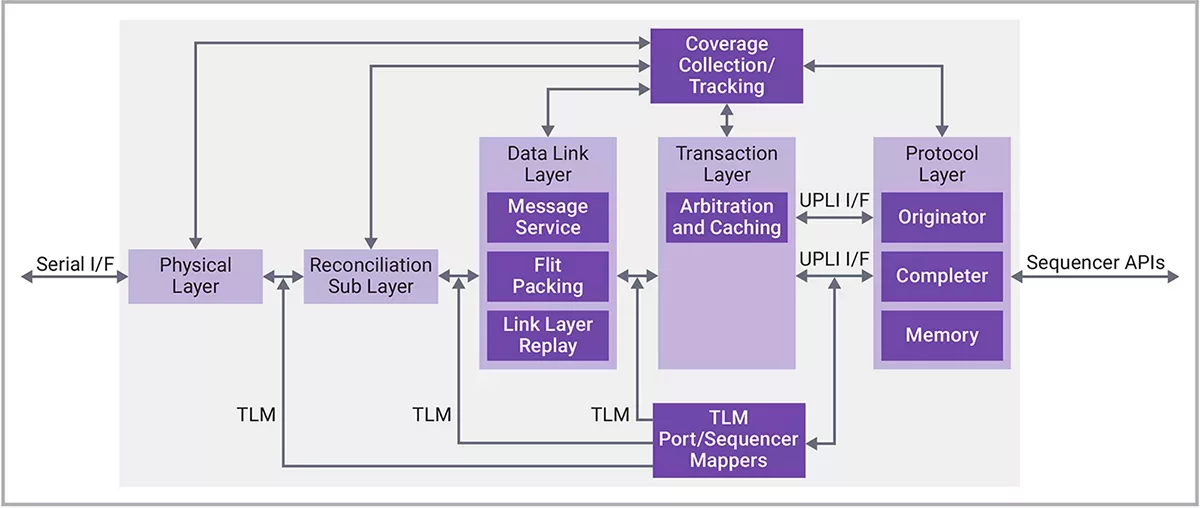

Specifications: UAL_200 1.0 Interfaces: 802.3 dj compliant, UPLI DUT Types/Topology: Protocol TL Phy DL Reconciliation Sub Layer…

Specifications: UAL_200 1.0

Interfaces: 802.3 dj compliant, UPLI

DUT Types/Topology:

Debug and Analysis:

Note: some files may require an NDA depending on provider policy.

Verification IP for UALink is a UALink IP core from Synopsys, Inc. listed on Semi IP Hub.

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UALink IP.

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.