Simulation VIP for UALink

The Ultra Accelerator Link (UALink) Verification IP (VIP) provides a bus functional model (BFM) with integrated automatic protoco…

Overview

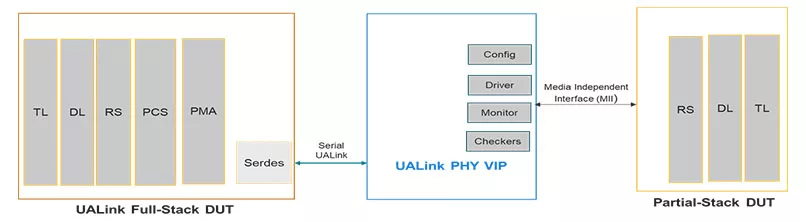

The Ultra Accelerator Link (UALink) Verification IP (VIP) provides a complete bus functional model (BFM) with integrated automatic protocol checks for physical layer in addition to Media Independent Interface (MII). Designed for easy integration in testbenches at IP, SoC, and system levels, the VIP helps engineers reduce time to first test, accelerate verification closure, and ensure end-product quality. The VIP for UALink can be used as a standalone PHY verification with jump-start test suite – Integration Test Suite (ITS) provided. The VIP for UALink supports a wide range of verification platforms, all major simulators, and the industry-standard Universal Verification Methodology (UVM). The VIP core is written in native C++ language for excellent performance, with seamless integration with verification languages. Supported specification: UALink 200G Rev1.0 specification

Supported specification: UALink 200G Rev1.0 specification

The following table lists the key features offered in the Cadence VIP for UALink:

|

Feature Name |

Description |

|---|---|

|

Device Type |

|

|

Interface |

|

|

Link Rate |

|

|

Link Width |

|

|

PMA Bus Width |

|

|

Bifurcation |

|

Key features

- Compliance to IEEE 802.3dj physical layer specification

- Verifies Standalone PHY DUT with x1, x2, x4 native widths and 100G, 200G, 400G, 800G speed

- 1-way, 2-way, 4-way interleaving supported

- Comprehensive protocol checks with 130+ built-in checks/assertions

- Serial and PMA bus widths listed at UALink level and MII between DL and PHY

- Callbacks access at multiple TX and RX queue points for scoreboarding and data manipulation

- Static and dynamic setting for configuration variables available

Block Diagram

Benefits

- Power-Efficient Design: Optimized for UALink

- Low-Latency: For maximum design performance

- Proven Solution: Full protocol stack implemented and verified in test chips

- Long-Reach Capability: Robust 224G 47+dB LR performance with LR/MR/VSR support at reduced power

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about UALink IP core

Validating UPLI Protocol Across Topologies with Cadence UALink VIP

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

UALink: Powering the Future of AI Compute

How Ultra Ethernet And UALink Enable High-Performance, Scalable AI Networks

Frequently asked questions about UALink IP cores

What is Simulation VIP for UALink?

Simulation VIP for UALink is a UALink IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this UALink?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this UALink IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.