Triple-speed (10Mbps/100Mbps/1Gbps) Ethernet Layer-2 switch that supports new protocols, providing seamless redundancy for Ethernet networking

The Flexibilis Redundant Switch (FRS) is a triple-speed (10Mbps/100Mbps/1Gbps) Ethernet Layer-2 switch that supports new protocol…

Overview

With its 1Gb speed and from 3 to 8 ports it is the highest performing HSR/PRP switch in the market. With FRS no separate RedBox is needed, but devices can be connected straight to the FRS, making it a cost-effective solution. Easy licensing method and free evaluation version are all available, as well as a very useful “Getting Started with FRS” training package. The training will help you to choose the correct functionalities for your needs.

Key features

- Triple-speed (10Mbps/100Mbps/1Gbps), full-duplex operation on all ports

- Compatible with IEC 62439-3 Clause 5 “High-availability Seamless Redundancy (HSR)”

- Compatible with IEC 62439-3 Clause 4 ”Parallel Redundancy Protocol (PRP)”

- Time and frequency synchronization using IEEE1588-2008 Precision Time Protocol v2

- Ethernet packet forwarding at wire-speed, non-blocking

- All of the ports of FRS can be either copper or fiber Ethernet interfaces, or connected to other FPGA blocks

- Ethernet packet filter and prioritization on each of the ports

- Reliable Store-and-Forward operation with data integrity checking

- HSR RedBox, HSR End-node, HSR QuadBox, PRP RedBox and DANP support

- IEEE1588v2 End-to-end one-step Transparent Clock Functionality

- IEEE1588v2 Peer-to-peer Transparent Clock support functions

- Compatible with IEEE standard 802.1D Media Access Control (MAC) Bridges

- Interface options – MII and GMII (RMII, RGMII and 1000BASE-X with separate adapters)

- Register interface for accessing control and status registers

- Management Data Input/Output (MDIO) controller for PHY and switch management, automatic polling of connected PHY devices

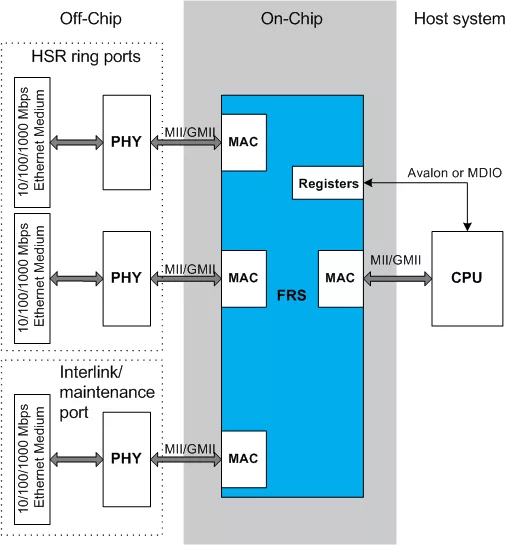

Block Diagram

Video

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is Triple-speed (10Mbps/100Mbps/1Gbps) Ethernet Layer-2 switch that supports new protocols, providing seamless redundancy for Ethernet networking?

Triple-speed (10Mbps/100Mbps/1Gbps) Ethernet Layer-2 switch that supports new protocols, providing seamless redundancy for Ethernet networking is a Ethernet IP core from Flexibilis Oy listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.