Simulation VIP for Ethernet UEC

Best-in-class Ethernet Verification IP for your IP, SoC, and System-level Design Testing The Cadence Verification IP (VIP) for Et…

Overview

Best-in-class Ethernet Verification IP for your IP, SoC, and System-level Design Testing

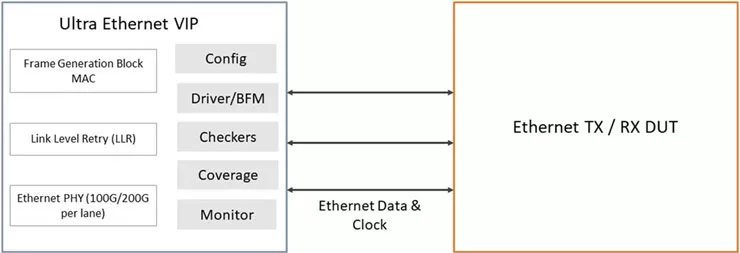

The Cadence Verification IP (VIP) for Ethernet UEC provides a mature, highly capable compliance verification solution for the Ultra Ethernet protocols stack, incorporating bus functional model (BFM) and integrated protocol checkers and coverage. The VIP for Ultra Ethernet is designed for easy integration in test benches at IP, system-on-chip (SoC), and system levels, helping to reduce time to test, accelerate verification closure, and ensure end-product quality. The VIP for Ultra Ethernet is compatible with the industry-standard Universal Verification Methodology (UVM) and runs on all leading simulators.

UEC is a family of protocols primarily of the data link layer and a couple of layers above it in the OSI Communication model, which delivers the ultra-low latency and high bandwidth necessary to connect a million nodes building a massive AI scale-out network and provides the interoperability and full communication stack architecture. These protocols are usually designed to work over a framework of Ethernet MAC and PHY layers.

Supported specifications: UEC-LLR Specification v0.82.

The following table shows key features from the specifications that are implemented in the VIP:

|

Feature Name |

Description |

|---|---|

|

Link Level Retry (LLR) |

|

Key features

- Support testbench language interfaces for SystemVerilog, UVM, OVM, e, and SystemC

- Callbacks access at multiple TX and RX queue points for scoreboarding, data manipulation, and error injection

- Transaction Tracker: Configurable tracking of all the transactions on the channels

- SystemVerilog coverage infrastructure for extendable coverage

- Predefined protocol checkers to evaluate the compliance of the DUT model to protocol requirements

Block Diagram

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is Simulation VIP for Ethernet UEC?

Simulation VIP for Ethernet UEC is a Ethernet IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.