Verification IP for Ultra Ethernet (UEC)

The Verification IP for Ultra Ethernet (UEC) provides a comprehensive set of protocol, methodology, verification and productivity…

Overview

The Verification IP for Ultra Ethernet (UEC) provides a comprehensive set of protocol, methodology, verification and productivity features, enabling users to achieve accelerated verification closure of Ethernet based designs.

VIP, based on its next-generation architecture and implemented in native SystemVerilog and UVM, runs natively on all major simulators. VIP can be integrated, configured and customized with minimal effort. Testbench development is accelerated with the assistance of built-in verification plans, functional coverage, example tests and comprehensive collection of sequences.

Key features

- Specifications: LLR 0.81, CBFC 0.8rc1

- Interfaces: 100G and above speeds

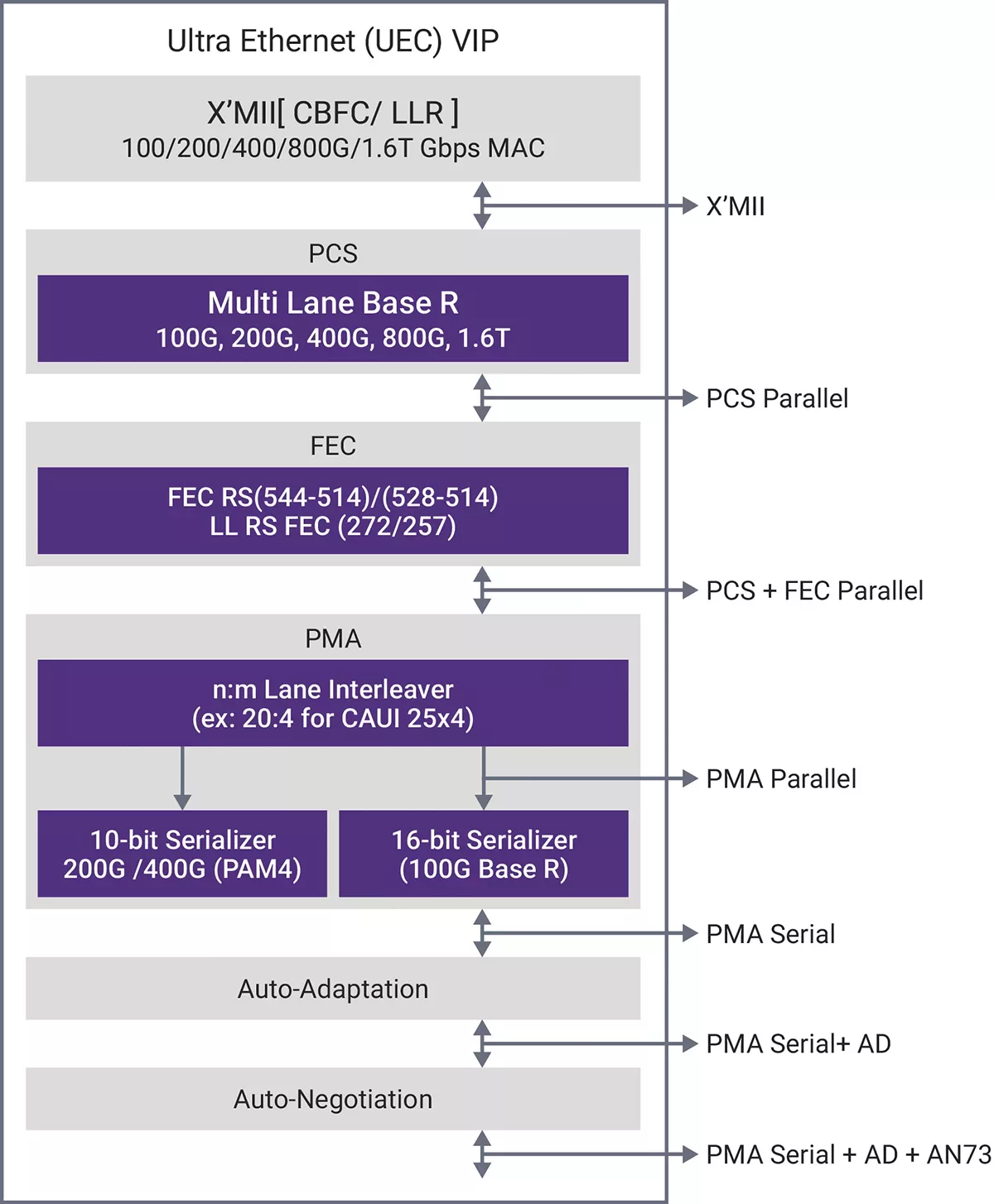

- DUT Types/Topology: multiple topologies for various DUT types such as X’MII DUT, PCS+PHY DUT, MAC+PCS+PHY DUT (Full Stack)

- Key VIP Features

- Specification linked Protocol checks and functional coverage

- Callback and Analysis ports for Scoreboard

- Configurable timers for threshold testing

- Reference example illustrating sanity usage and representative protocol scenarios

- Provide hooks via callbacks for error injection

- Separate Analysis ports for LLR frames and Ctlos

- Can be used in Active as well as in Passive mode

- Debug and Analysis

- Verdi based protocol and performance analysis

- Protocol checks at each layer

- Key Protocol Features:

- Transaction attributes for modelling various traffic profiles related to CBFC and LLR

- Configuration attributes for finer control over interface characteristic such as rate and mode of operation

- Supported Use-cases

- Transmission of LLR eligible/ineligible frames

- Configurable replay timers

- Transmission of all 4 Ctlos.

- CBFC flow control

Block Diagram

Benefits

- Native SystemVerilog/UVM

- Source code test suite including UNH-IOL (optional)

- Runs natively on major simulators

- Built-in protocol checks

- Verification plan and coverage

- Verdi® Protocol & Performance Analyzer

- Trace file support for debugging

- Extensive error injection

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Ethernet IP core

UA Link PCS customizations from 800GBASE-R Ethernet PCS Clause 172

Three Ethernet Design Challenges in Industrial Automation

Verification of UALink (UAL) and Ultra Ethernet (UEC) Protocols for Scalable HPC/AI Networks using Synopsys VIP

Powering Scale Up and Scale Out with 224G SerDes for UALink and Ultra Ethernet

Ultra Ethernet Security: Protecting AI/HPC at Scale

Frequently asked questions about Ethernet IP cores

What is Verification IP for Ultra Ethernet (UEC)?

Verification IP for Ultra Ethernet (UEC) is a Ethernet IP core from Synopsys, Inc. listed on Semi IP Hub.

How should engineers evaluate this Ethernet?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Ethernet IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.