Stream Direct Memory Access (SDMA)

The multi-channel Stream Direct Memory Access (SDMA) controller IP core provides high bandwidth direct memory access between memo…

Overview

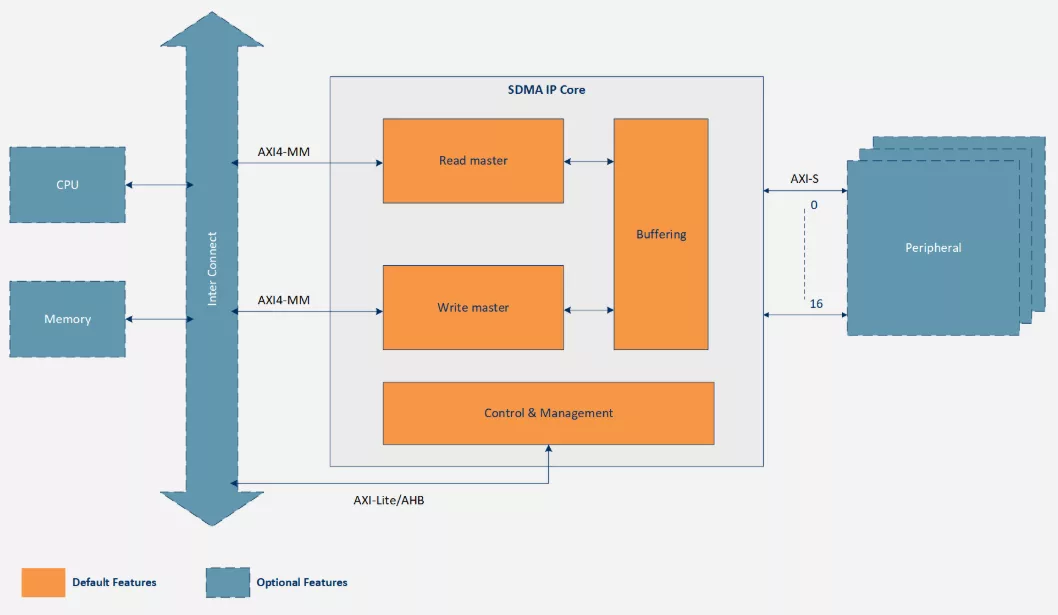

The multi-channel Stream Direct Memory Access (SDMA) controller IP core provides high bandwidth direct memory access between memory and any IP peripherals with an AXI4-Stream interface for up to 16 channels.

The SDMA IP utilities a dedicated Write and Read circular buffer structure for data and descriptor(s) for each DMA channel, which helps in offloading data movement tasks from the Central Processing Unit (CPU) in processor-based systems.

Configuration of status and management registers are accessed through an AXI4-Lite interface. Control and Status streaming interfaces are used for sending/receiving user application data. Interrupts are available to indicate error and completion events.

Key features

Delivering Performance

- AXI4-Streaming compliant user interface

- 1–16 independent DMA channels supporting bi-directional data transfers

- Driver for Linux platform is available

Highly Configurable

- Circular buffer structure for data and descriptors with configurable size

- Supports Memory-Peripheral and Peripheral-Memory

Easy to use

- Silicon proven

Silicon Agnostic

- Designed in SystemVerilog and targeting both ASICs and FPGAs

Block Diagram

What’s Included?

The IP Core can be delivered in Source code or Encrypted format. The following deliverables will be provided with the IP Core license:

- Solid documentation, including User Manual and Release Note

- Simulation Environment, including Simple Testbed, Test case and Test Script

- Programming Register Specification

- Timing Constraints in Synopsys SDC format

- Access to support system and direct support from Comcores Engineers

- Synopsys SGDC Files (optional)

- Synopsys Lint, CDC and Waivers (optional)

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about DMA IP core

Using peripheral DMA boosts networked 32 bit MCU security and bandwidth

New AXI Scatter-Gather DMA Core Transfers Streaming Data to/from System Memory

Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

Considerations When Architecting Your Next SoC: NoCs with Arteris

Can Your NPU Run DOOM? Chimera Can.

Frequently asked questions about DMA IP

What is Stream Direct Memory Access (SDMA)?

Stream Direct Memory Access (SDMA) is a DMA IP core from Comcores listed on Semi IP Hub.

How should engineers evaluate this DMA?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DMA IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.