DMA Unit

Up to 64 byte data transfer in CAN FD frames The DMU signals to the attached DMA Controller (DMA request) when there is a newly r…

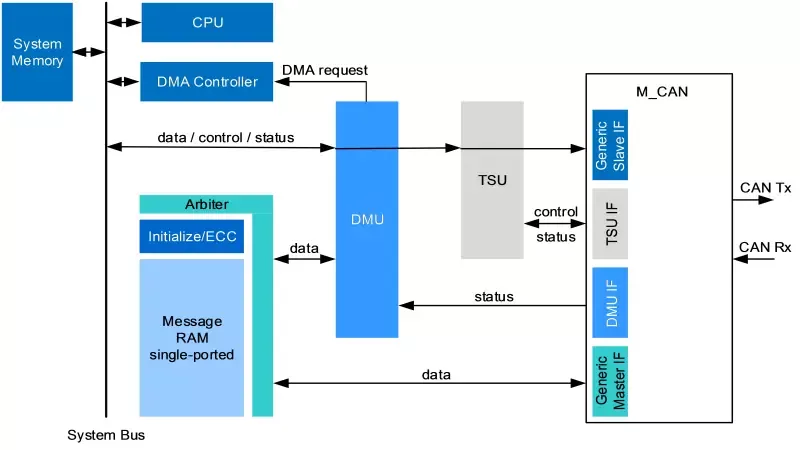

Overview

Up to 64 byte data transfer in CAN FD frames

The DMU signals to the attached DMA Controller (DMA request) when there is a newly received message available at one of the attached M_CAN's Rx FIFOs respectively when there is the possibility to load a new Tx message into the M_CAN's Tx FIFO/Queue.

The DMA controller then autonomously transfers the received message from the M_CAN's Message RAM to the System Memory or the message to be transmitted from the System Memory to the M_CAN's Message RAM.

After the DMA transfer has completed, the DMU acknowledges this to the M_CAN's Rx FIFO respectively sets the related M_CAN's transmission request.

Key features

- Enables real-time control loops

- Deterministic multi-threaded architecture (8 threads per RISC unit)

- Programmability (special purpose RISC/ALU)

- Scalable and configurable architecture

- Easy integration due to generic interfaces and hierarchical architecture

- SystemC model support for in-system verification and early software development

- Supports model-based development

- 5 ns input and output resolution for high-precision data capturing and data signal generation

Block Diagram

Benefits

- Offloads tasks from the CPU to the DMA controller

- Enables DMA transfers of M_CAN FIFO elements and optional TSU timestamps between Message RAM and system memory.

- Available for integration into microcontrollers, ASICs, and FPGAs.

What’s Included?

- VHDL source code,

- test environment (test bench and integration tests),

- SystemC executable model for in-system verification and early software development,

- documentation,

- application notes,

- serial communication protocol software drivers

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about DMA IP core

Using peripheral DMA boosts networked 32 bit MCU security and bandwidth

New AXI Scatter-Gather DMA Core Transfers Streaming Data to/from System Memory

Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

Considerations When Architecting Your Next SoC: NoCs with Arteris

Can Your NPU Run DOOM? Chimera Can.

Frequently asked questions about DMA IP

What is DMA Unit?

DMA Unit is a DMA IP core from Robert Bosch GmbH listed on Semi IP Hub.

How should engineers evaluate this DMA?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DMA IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.