Multi-Channel AXI DMA Engine

The Multi-Channel AXI DMA engine IP Core for AXI4 is a programmable AXI Stream to AXI memory mapped bridge with sophisticated dat…

Overview

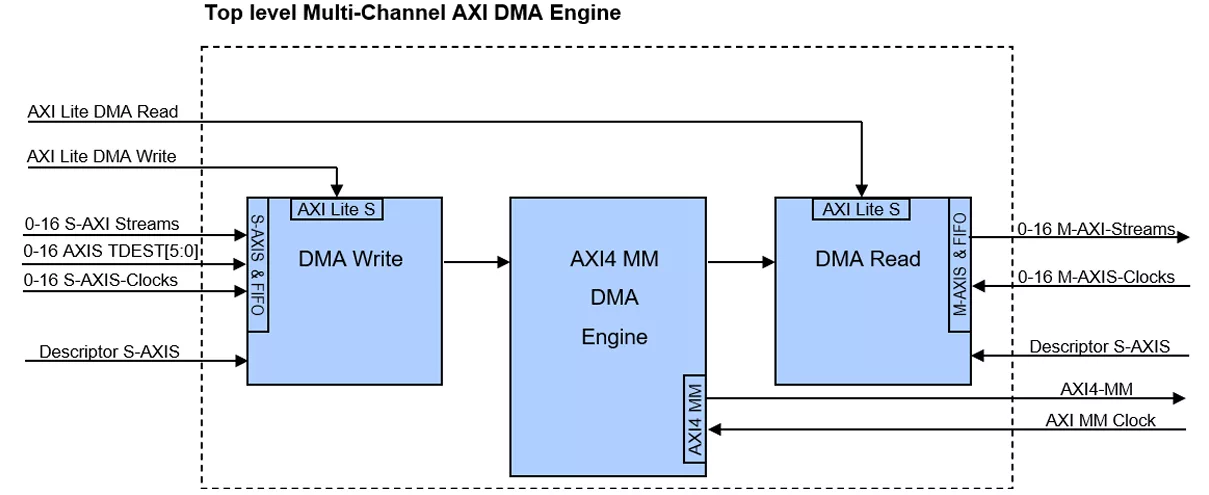

The Multi-Channel AXI DMA engine IP Core for AXI4 is a powerful programmable AXI Stream to AXI memory mapped bridge with sophisticated data addressing options. These features allow data accesses on a tile basis in order to address regions of interest (ROI) based applications like stereo cameras, 2D picture compression algorithms and others.

Up to 16 independent AXI Stream Slaves write DMA data to the connected AXI Slaves. Up to 16 AXI Stream Masters read DMA data from the connected slaves and present it to the user logic. Each channel operates in its own address map. This IP core targets continuous data streaming applications (i.e. data acquisition, Video and DSP applications) with AXI Stream interfaces and is well suited for standard AXI4 Slaves including DDR Memory Interfaces or the AMD ZynqTM devices. A sophisticated Linux kernel mode device driver allows easy data access from user mode.

Key features

- Multi-channel architecture

- Non-blocking approach, an incomplete AXI Stream packet does not block other AXI Streams

- Up to 16 AXI Stream Slave interfaces that can address up to 64 destinations

- Up to 16 AXI Stream Master interfaces

- Independent clocking and data width for each AXI Stream interface

- Configurable via 2 AXI Lite or AXI Stream interfaces

- Linux Kernel mode driver included

- Powerful addressing schemes supported: Ascending, descending and streaming into or from regions of interest (ROI)

- Memory size up to 4 GByte per streaming channel

- GStreamerTM compatible

- Available for all AMD, Altera and Lattice devices

Block Diagram

Applications

- The Multi-Channel AXI DMA Engine is often used with SoC based FPGAs where AXI Stream / Avalon Stream based data streams like camera data or A/D converter data have to be streamed into the DDR of the SoC. The included Linux driver with its high-level user mode library allows fast and very easy access to the data. The compatibility of the driver with GStreamer provides the user with a very powerful open-source video framework for further processing.

- This IP core is also used in non-SoC based FPGAs, for example when DDR memory is required as a data buffer.

What’s Included?

- Encrypted VHDL Source Code for easy Designflow integration

- Comprehensive User Guide

- Reference Design

- Windows / Linux Driver Package (Option)

- PCI-Express Testbench with High Speed simulation mode

- Technical support

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about DMA IP core

Using peripheral DMA boosts networked 32 bit MCU security and bandwidth

New AXI Scatter-Gather DMA Core Transfers Streaming Data to/from System Memory

Area, Pipelining, Integration: A Comparison of SHA-2 and SHA-3 for embedded Systems.

Considerations When Architecting Your Next SoC: NoCs with Arteris

Can Your NPU Run DOOM? Chimera Can.

Frequently asked questions about DMA IP

What is Multi-Channel AXI DMA Engine?

Multi-Channel AXI DMA Engine is a DMA IP core from Smartlogic GmbH listed on Semi IP Hub.

How should engineers evaluate this DMA?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this DMA IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.