Simulation VIP for DisplayPort

Used by market leaders driving the specification.The Cadence® Verification IP (VIP) for DisplayPort is the industry's most compre…

Overview

Used by market leaders driving the specification.

The Cadence® Verification IP (VIP) for DisplayPort is the industry's most comprehensive protocol validation solution for DisplayPort designs. It provides a complete bus functional model (BFM) and protocol monitor with integrated automatic protocol checks. Incorporating the latest protocol updates, the DisplayPort VIP is designed for easy integration in testbenches at IP, SoC, and system levels, the VIP helps engineers reduce time to first test, accelerate verification closure, and ensure end-product quality.

The VIP for DisplayPort can be used as standalone, as a platform for running TripleCheck tests, and/or enabling DSC VIP on top of the base VIP. The VIP for DisplayPort is compatible with all main verification languages such as Verilog, SystemVerilog, e, VHDL, C, SystemC®, and Vera, methodologies such as UVM, OVM, and VMM, and runs on all leading simulators.

Supported specifications: VESA DisplayPort versions 1.2a, 1.3, 1.4, 1.4a, 2.0, and 2.1 and Embedded DisplayPort (eDP) versions 1.3, 1.4a, 1.4b, and 1.5.

Key features

- Device Support

- Source, Sink, Link Training-Tunable PHY Repeater (LTTPR/retimer)

- Main Link Interface

- Serial, Parallel (10-bit, 20-bit, 40-bit)

- Link Rate

- RBR (1.62Gbps), HBR (2.7Gbps), HBR2 (5.4Gbps), R216 (2.16Gbps), R243 (2.43Gbps), R324 (3.24Gbps), R432 (4.32Gbps), UHBR10 (10Gbps), UHBR13.5: (13.5Gbps), UHBR20 (20Gbps)

- Link Width

- Configurable link width support: x1, x2, and x4 lane

- AUX

- Native AUX, I2C over AUX, AUX Manchester-II encoding, AUX jitter generation and detection

- HDCP

- Protocol Versions: 1.3, 2,2, 2,3

- Authentication protocol

- Cipher and data encryption/decryption

- Link integrity check in SST and MST

- Encryption status signaling

- Allow AUX_DEFER as a valid response

- DPCD

- Provides support for DisplayPort Configuration Data

- HPD

- Plug, Unplug and IRQ pulse

- Isochronous Transport Services

- Single-Stream Transport (SST) and Multi-Stream Transport (MST) modes

- Video Formats/Modes

- All bit depth via pixel arrays

- Color formats: YCbCr 4:2:0, RAW bpp 6/7/8/10/12/14/16, Adaptive-Sync and ignore MSA, MISC 1-bit 6 support

- Interlaced video mode

- Audio

- LPCM non-HBR, LPCM HBR, 3D LPCM, 1-bit, DST, INFOFRAME SDP, Audio_TimeStamp SDP

- Link Training

- Adjustable swing levels

- Adjustable pre-emphasis levels

- Link retraining

- Fast training without AUX handshakes

- Main Link Modeling

- Physical Layer

- (De)serialization (8b/10b, 128b/132b)

- Scrambling/descrambling

- (De)serialization (8b/10b, 128b/132b)

- (De)skewing

- Error Correcting Code (ECC)

- Forward Error Correcting (FEC)

- 16-bit CRC for each color component

- Link Layer (Frames, Lines, Idles)

- Color (un)packing

- (Un)stuffing

- (Un)framing (basic and enhanced)

- Forward Error Correction (FEC)

- With SST/MST and with or without HDCP:

- Reed-Solomon (RS) 254, 250

- Two-way interleaving and de-interleaving (CD_ADJ, FEC_PM)

- Spread Spectrum Clocking (SSC)

- DP 1.4, DP2.0

- Link Quality Patterns

- Nyquist

- Symbol Error Rate

- PRBS7

- HBR2 EYE patterns

- Custom 80-bit

- Custom 264-bit

- Mixed patterns on different lanes

- Power Management

- Enables Sink power state machine and power-save mode

- Advanced Link Power Management (ALPM) to reduce wake-up latency

- Global Time Code

- Enabled synchronization between DP devices across a DP link to a 100ns precision

- Panel Self Refresh (PSR)

- PSR, PSR2

- DisplayPort 2.0, 2.1

- Link Training

- Concurrent Link Training

- Encoding

- 128b/132b channel encoding

- Serialization/De-serialization Update

- Serialization/De-serialization of 128b/132b encoding

- Scrambling

- Scrambling/De-scrambling for new 128b/132b encoding

- Multi-stream Transport (MST) Mode Updates

- MST used for transporting multiple main video streams each enclosed in a VC payload

- Up to 63 independent audio video streams

- SDP splitting by default

- Link Rate Updates

- New link rates: UHBR10 (10Gbps/lane), UHBR13.5 (13.5Gbps/lane), UHBR20 (20Gbps/lane)

- PHY Logical Updates

- Link Layer to PHY logical main link lane count conversion

- Intra super symbol shifting/reverse shifting

- Link Layer and Link Training Updates

- 128b/132b TPS's and sequence

- SDP parity nibbles zero-padding (deprecate nibble interleaving)

- VFREQ and AFREQ replacement

- Panel Replay Mode

- Optional feature defined as a subset of Panel Self Refresh 2 mode to reduce system level power and increase flexibility of adaptive sync solution.

- Data Stream Compression (DSC) Updates

- DSC support mandate for 128b/132b Link Layer-capable DP devices

- DSC bitstream pass-through across DP branch device (retimer)

- DSC bitstream mapping to 32-bit link symbol

- Control Data Indicator (CDI)

- CDI insertion

- Combine 4-bit CDI + four 32-bit symbols to 132-bit symbols

- Precoding

- Pre-coding is default enabled and can be disabled for 128b/132b channel coding

- Skew

- TX skew (up to 32-bit between lanes)

- RX deskew

- Forward Error Correction (FEC) Updates

- Two-way interleaving and de-interleaving, RS FEC enablement

- Link Layer Lane Count

- 4

- Physical Lane Count

- 4, 2, 1

- Micro-Packet

- Multi-stream transport packet (MTP)

- 64 link symbol cycles per Link Layer Lane

- Condensed micro-packet header in Link Layer Control Packet (LLCP)

- Link Layer Frame Boundary Update

- Link Layer Control Packet (LLCP) for 128b/132b encoding

- Link Quality Pattern Updates

- Nyquist pattern, Square pattern, SymbolErr (128b/132b TPS2), 264b custom, Mixed patterns on different lanes

- Fallback

- Fallback from DP 2.0 to DP 1.4

- DisplayPort 1.3 1.4,1.4a

- Video Format Update

- YCbCr 4:2:0, RAW bpp 6/7/8/10/12/14/16, Adaptive-Sync and ignore MSA, MISC 1-bit 6 support

- SDP Format Update

- Camera SDP

- VSC SDP extension for Pixel Encoding and Colorimetry Format

- Video Stream Configuration Extension VESA (VSC_EXT_VESA) chain-able SDP type

- Video Stream Configuration Extension CEA (VSC_EXT_CEA) chain-able SDP type

- CEA InfoFrame SDP packing format Ver.1.3

- Picture Parameter Set SDP

- SDP Splitting in SST and MST mode

- Audio Format Update

- Native support for 3D LPCM, One Bit, and DST types

- Forward Error Correction (FEC)

- Support for following with SST/MST and with/without HDCP

- Reed-Solomon code FEC function RS (254, 250)

- Two-way interleaving, CD_ADJ, FEC_PM

- FEC SCRs

- FEC decode enable sequence re-enable 1,000LL

- FEC enable sequence first enable 1,000LL after LT

- FEC decode sequence insertion at the end of FEC block

- PM symbol not to advance the HDCP cipher

- FEC running disparity change

- Link Training Update (+SCRs)

- HBR3 - 8.1Gbps/lane speed

- TPS4 pattern

- Post-Link training request sequence and fallback support

- Total of 10 AUX_ACKs for read request

- Symbol lock failures in two- and four-lane configurations

- Reduced lane fallback during CR

- Last partial TPS2/TPS3/TP4 training patterns

- Link Quality Measurement Pattern Update

- CP2520 (HBR2 Compliance EYE pattern) SR-CP-CP-SR-248 00h's, SR-BF-BF-SR-248 00h's, SR-BS-BS-SR-248 00h's

- Link Training-Tunable PHY Repeater

- Source and Sink model support LTTPR

- eDP

- Content Protection

- TPS4 with Alternative Scrambler Seed Reset (ASSR)

- HDR Support Update

- New SDP packets to support HDR (VCS Extension VESA SDP and VCS Extension CEA SDP)

- SDP Format Update

- SDP splitting for SST mode

- Backlight Control

- Enables Backlight and Display control registers

- Display Authentication

- Alternative Scrambler Seed Reset (ASSR)

- Fast Training

- Fast training without AUX handshakes

- PSR / PSR2

- Provides the ability for Panel Self Refresh (PSR)

- ALPM

- Supports Advanced Link Power Management (ALPM) to reduce wakeup latency

- Link Rate

- Supports new standard link rates: R216 (2.16Gbps), R243 (2.43Gbps), R324 (3.24Gbps), and R432 (4.32Gbps) for system optimization

- Aux Frame Sync

- AUX-based Source-to-Sink Device Active Video Timing Synchronization

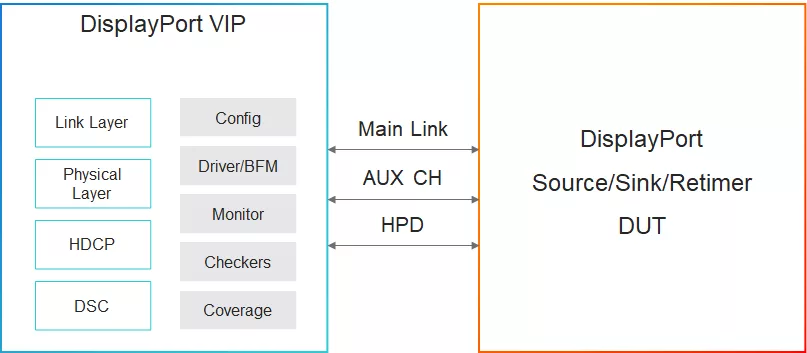

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Displayport IP core

VESA Adaptive-Sync V2 Operation in DisplayPort VIP

Understanding LTTPR: Enabling High-Speed DisplayPort Interconnects in Complex System Designs

DisplayPort 2025: Navigating the Next Wave of Display Innovation

Audio Transport in DisplayPort VIP

DisplayPort 2.1 vs DisplayPort 1.4: A Detailed Comparison of Key Features

Frequently asked questions about DisplayPort IP cores

What is Simulation VIP for DisplayPort?

Simulation VIP for DisplayPort is a Displayport IP core from Cadence Design Systems, Inc. listed on Semi IP Hub.

How should engineers evaluate this Displayport?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Displayport IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.