PLL

The high performance PLL is a high speed, low jitter frequency synthesizer, developed as an IP block to reduce time to market, ri…

Overview

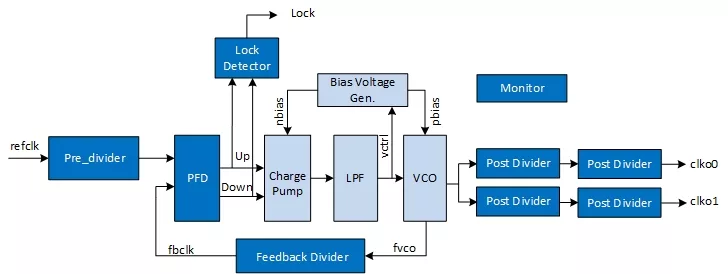

The high performance PLL is a high speed, low jitter frequency synthesizer, developed as an IP block to reduce time to market, risk, and cost in the development of Analog Front-End design. It can generate a stable high-speed clock from an ultra-wide input clock. With excellent supply noise immunity, the PLL is ideal for use in noisy mixed signal SoC environments. This PLL integrates a Phase Frequency Detector (PFD), a Low Pass Filter (LPF), a Voltage Controlled Oscillator (VCO), and other associated circuits. All fundamental building blocks and programmable dividers are integrated in the core.

The low-power Fractional-N/SSCG PLL addresses power-sensitive applications. It supports non-integer clock multiplication, programmable clock synthesis, on-the-fly clock tracking or fine tuning, and spread spectrum clock generation. Designed for digital logic processes, the PLL incorporates robust design techniques to operate reliably in noisy SoC environments, such as high-speed communication systems, low power consumer devices, and memory interfaces.

Key features

- Supports frequencies from 1GHz to 3.2GHz for versatile applications

- Low jitter performance

- Supports Fractional mode to enable fine frequency resolution for precise tuning

- Supports SSC mode to reduce EMI

- Supports multiple frequencies and phases

- Input reference clock frequency is supported ranging from 10MHz to 500MHz

- Built-in lock detector to indicate the frequency lock state

Block Diagram

Benefits

- Low power consumption

- Low jitter

- Wide frequency range

- Small area

Applications

- Microprocessors and Microcontrollers

- FPGAs and ASICs

- RF Transceivers

- Serial Data Communication

- Audio/Video Systems

- Consumer Electronics

- Automotive Electronics

- Radar and Sonar Systems

- IoT Devices

- Advanced Driver Assistance Systems

- Consumer Electronics

What’s Included?

- GDSII

- CDL Netlist (MG Calibre Compatible)

- Functional Verilog Model

- Liberty timing models (.lib)

- LEF

- Application Note

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about PLL IP core

CoreHW Develops 80GHz mmWave PLL with Synopsys RFIC Design Flow on GlobalFoundries 22FDX Technology

Specifying a PLL Part 3: Jitter Budgeting for Synthesis

Specifying a PLL Part 2: Jitter Basics

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Achieving Groundbreaking Performance with a Digital PLL

Frequently asked questions about PLL IP cores

What is PLL?

PLL is a PLL IP core from Innosilicon Technology Ltd listed on Semi IP Hub.

How should engineers evaluate this PLL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PLL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.