General use, integer-N 4GHz Hybrid Phase Locked Loop on TSMC 28HPC

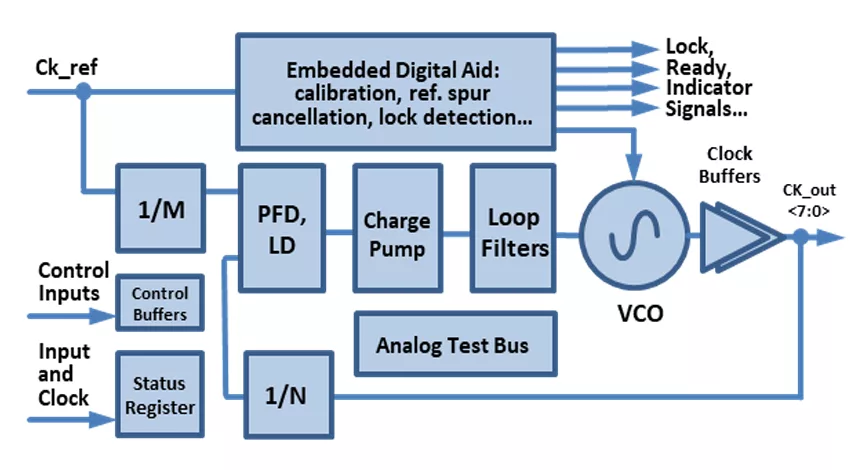

This Integer-N Hybrid (Digitally Aided Analog) PLL generates clock signals within broad frequency range.

Overview

This Integer-N Hybrid (Digitally Aided Analog) PLL generates clock signals within broad frequency range. Division coefficients of the embedded input and feedback dividers can be set to any integer between 1 and 64 or may be bypassed to save power. Higher order dividers and/or pre-scalers are optional. Output clock may be 8- or 4-phase set by the user. Disabling 4 out of 8 output buffers also saves power. With use of external frequency multipliers, the output clock frequency may be doubled or quadrupled. User controlled embedded control register allows setting frequency division, loop bandwidth, phase margin, peaking. PLL has reference spur reduction functions also controlled by the control register. The control register has serial and parallel interfaces. This PLL has very short lock time, lock indicator signal and power-up sequence support signals. Footprint is compact and no off-chip components are needed. This PLL has Analog Test Bus (ATB) as a Design for Test (DFT) feature.

Key features

- Output frequency range: 500MHz ÷ 2GHz

- Reference clock frequency range: 8MHz ÷ 2GHz

- User-set 4 or 8 output clock phases

- Loop bandwidth 60kHz - 180MHz, with phase margin >50°

- Output clock duty cycle 50 +5%

- Typically locks within 150 reference clock cycles

- Simple power-up sequence facilitated by indicator output signals

- All digital aid functions are embedded, minimum external control is required

- Embedded control register with serial and parallel interfaces

- Input for external ROM storing multiple pre-set states

- Typical supply voltage 900mV

- All input and output signals are CMOS

- Typical power consumption: 2.6mA at 1GHz, scales with VCO frequency

- Low leakage power down mode

- Operational temperature: -40°C to +110°C

- Footprint: 150 x 200 µm

- Does not require any off-chip components

- Design For Test (DFT) enabled by embedded Analog Test Bus (ATB)

- Process: TSMC 28nm HPC/HPC+, design can be ported to other nodes

Block Diagram

Applications

- This general purpose PLL generates and synthetizes clock signals for a broad range of applications, such as telecommunication, consumer, automotive, industrial etc., where compact footprint, low power, very fast locking and high functional flexibility are needed while use of external components should be avoided.

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 28nm | HPC | — |

Specifications

Identity

Provider

Learn more about PLL IP core

CoreHW Develops 80GHz mmWave PLL with Synopsys RFIC Design Flow on GlobalFoundries 22FDX Technology

Specifying a PLL Part 3: Jitter Budgeting for Synthesis

Specifying a PLL Part 2: Jitter Basics

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Achieving Groundbreaking Performance with a Digital PLL

Frequently asked questions about PLL IP cores

What is General use, integer-N 4GHz Hybrid Phase Locked Loop on TSMC 28HPC?

General use, integer-N 4GHz Hybrid Phase Locked Loop on TSMC 28HPC is a PLL IP core from Kamaten Technology Incorporated listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this PLL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PLL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.