Overview

The TRC16024CPA is a four lane Gen 1,2,3,4 PCI Express Physical layer (Phy) Phy IP core, delivering high-speed serial data transmission over controlled impedance transmission media such as copper cable, PCB traces or fiber optics. The device offers support for 2.5/5.0/8.0/16 Gbps PCI Express which include spread spectrum clocking, beacon out of band signaling and deemphasis support. TRC16024CPA operates on 0.8/1.8 V supplies. The IP is capable of transmitting and receiving serial data at 2.5,5.0,8.0,16 Gbps per lane with excellent bit error rate performance.

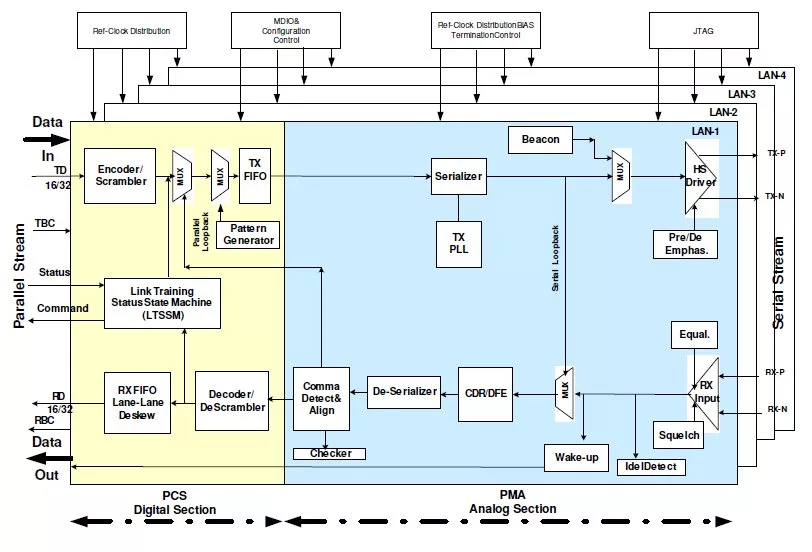

Each transmit section of the TRC16024CPA contains a low-jitter clock synthesizer, a parallel to serial converter with built in PCS transmit functions, and a CMOS output driver with selectable de-emphasis for use in backplane applications.

Each receive section contains an input limiting amplifier with on-chip terminations and selectable equalization levels, clock/data recovery PLL, and PCS receive functions. Built-in serial and parallel loopback modes. PRBS generator/checker and error detectors aid in support of testing.

The TRC16024CPA requires no external components for its clock synthesizers and clock recovery PLL. Three external resistors are needed to set the proper bias currents for its onchip terminations.

TRC16024CPA has low jitter generation and high jitter tolerance making it ideal for integration in SoCs and ASICs in the presence of multiple clocks and noise. TSMC is available in TSMC 16 nm FFC process and can be ported to other processes.

Learn more about Single-Protocol PHY IP core

UniversalFlash Storage (UFS) was created for mobile applications and computer systems requiring high performance and low power consumption. These systems typically use embedded Flash based on the JEDEC standard eMMC. UFS was defined by JEDEC as the evolutionary replacement for eMMC offering significantly higher memory bandwidth. The standard builds on existing standards such as the SCSI command set, the MIPI Alliance M-PHY and UniPro as well as eMMC form factors to simplify adoption and development.

In this paper, we introduce a new high-level, dataflow programming language called C~ (“C flow”) that further increases productivity by raising the level of abstraction from behavioral descriptions, while overcoming the limitations of C for hardware design. We present the syntax and semantics of this language, and the framework that provides hardware and software code generation. This paper illustrates the benefits of using C~ for hardware design of a IEEE 802.3 MAC, synthesized for FPGA and for 90nm CMOS technology.

Universal Flash Storage (UFS) was created for mobile applications and computer systems requiring high performance and low power consumption. These systems typically use embedded Flash based on the JEDEC standard eMMC. UFS was defined by JEDEC as the evolutionary replacement for eMMC offering significantly higher memory bandwidth. The standard builds on existing standards such as the SCSI command set, the MIPI Alliance M-PHY and UniProSM as well as eMMC form factors to simplify adoption and development.

Since MIPI and MDDI standards both target interfaces to cameras and displays on mobile devices, are two separate standards really needed?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization