1.25 Gbps LVDS IPs library

028TSMC_LVDS_01 is a library including: Transmitter LVDS driver (TX_LVDS); Receiver LVDS driver (RX_LVDS); Reduced range link rec…

Overview

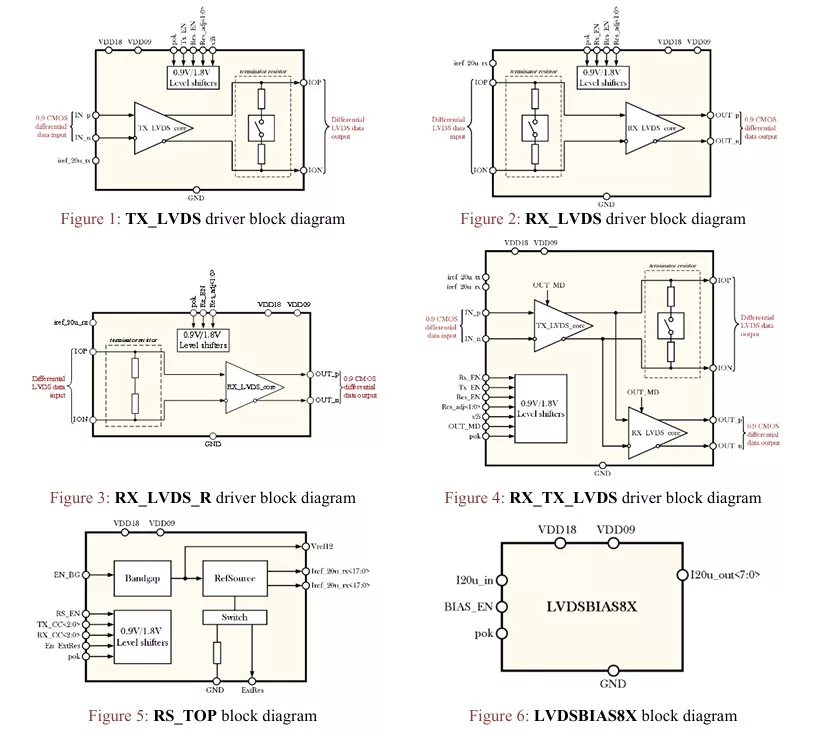

028TSMC_LVDS_01 is a library including:

- Transmitter LVDS driver (TX_LVDS);

- Receiver LVDS driver (RX_LVDS);

- Reduced range link receiver LVDS driver (RX_LVDS_R);

- Transceiver LVDS driver (RX_TX_LVDS);

- Reference current/voltage generators (RS_TOP);

- Bias block (LVDSBIAS8X) for 8 LVDS drivers

RX_TX_LVDS driver has five available operation modes: transmitter, receiver, transmitter half-duplex, receiver half-duplex and shutdown. The RS_TOP block is intended to output reference currents and voltage for RX_LVDS, RX_LVDS_R, TX_LVDS and TX_RX_LVDS drivers as well as for bias block. Composing of LVDS library components allows to design a device with up to 16 pairs of data channels and 2 pairs of synchronization channels.

Key features

- TSMC 28nm CMOS

- TIA/EIA-644 LVDS standards without hysteresis

- Data transfer rate: 1250Mbps

- 1.8V IO voltage supply

- 0.9V core voltage supply

- 0.9V CMOS input/output logic control signals

- 0.9V/1.8V level shifters

Block Diagram

Applications

- Point-to-point data transmission

- Multidrop buses

- Clock distribution

- Backplane receiver

- Backplane data transmission

- Cable data transmission

What’s Included?

- Schematic or NetList

- Abstract model (.lef and .lib files)

- Layout view (optional)

- Behavioral model (Verilog)

- Extracted view (optional)

- GDSII

- DRC, LVS, antenna report

- Test bench with saved configurations (optional)

- Documentationn

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 28nm | 28nm 280 nm | Pre-Silicon |

Specifications

Identity

Files

Note: some files may require an NDA depending on provider policy.

Provider

Learn more about Single-Protocol PHY IP core

Design IP Faster: Introducing the C~ High-Level Language

Universal Flash Storage: Mobilize Your Data

Can MIPI and MDDI Co-Exist?

Enter the Inner Sanctum of RapidIO: Part 1

Networking software key to PICMG 2.16 optimization

Frequently asked questions about Single-Protocol PHY IP

What is 1.25 Gbps LVDS IPs library?

1.25 Gbps LVDS IPs library is a Single-Protocol PHY IP core from NTLab listed on Semi IP Hub. It is listed with support for tsmc Pre-Silicon.

How should engineers evaluate this Single-Protocol PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Single-Protocol PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.