MIPI SOUNDWIRE PSVIP

MIPI SoundWire Post Silicon Validation IP provides a smart way to post silicon validation of the MIPI SoundWire component of a SO…

Overview

MIPI SoundWire Post Silicon Validation IP provides a smart way to post silicon validation of the MIPI SoundWire component of a SOC. MIPI SoundWire Post Silicon Validation IP provides an smart way to post silicon validation of the MIPI Soundwire bus. The SmartDV's MIPI SoundWire Post Silicon Validation IP is fully compliant with version 1.2r08 MIPI SoundWire Bus Specification and provides the following features.

MIPI SOUNDWIRE PSVIP is supported natively in SystemVerilog, VMM, RVM, AVM, OVM, UVM, Verilog, SystemC, VERA, Specman E and non-standard verification env

MIPI SOUNDWIRE PSVIP comes with optional Smart Visual Protocol Debugger (Smart ViPDebug), which is GUI based debugger to speed up debugging.

Key features

- Supports MIPI SoundWire version 1.2r08 Specifications

- Supports full MIPI SoundWire Master,Slave functionality

- Supports Basic PHY and High PHY mode

- Supports IO timing

- Supports all frame shapes

- Supports static, dynamic and PHY frame synchronization

- Supports handling over bus control to Monitor based on BREQ bit

- Supports BANK handling

- Supports handling of all combinations of ACK/NACK responses

- Supports PING, Read, Write commands

- Supports all registers definitions with proper read/write attributes

- Supports Dual Ranked Register and Commit mechanism

- Supports Multi-byte Quantities buffer

- Supports dynamic shape and payload switching

- Supports groups and group response generation and handling

- Supports bulk payload transport and bulk register access

- Supports PRBS, Static0 and Static1 test modes

- Supports clock pause and clock stop operation

- Supports various kind of interrupts

- Supports multi-lane payload transport

- Supports various kind of payload positioning w.r.t Block per port and Block per channel

- Supports various kind of flow controlled payload transport

- Supports various kind of resets

- Bus-Reset

- ClockStopMode1 Reset

- LostSync Reset

- Register Reset

- Supports various kind of Master and Slave errors generation

- Parity errors

- CRC errors

- Dynamic Sync bit errors

- Static sync bit errors

- Slave responding when address not assigned

- Master startup using wrong shape

- Bus clash error

- PRBS pattern error

- Testmode Static 0 error

- Testmode Static 1 error

- Supports bus-accurate timing.

- Supports programmable speed.

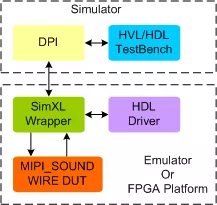

Block Diagram

Benefits

- Runs in custom FPGA platforms

- Validate MIPI Soundwire device for compliance

What’s Included?

- Linux Perl Driver to control the PSVIP

- Encrypted RTL of PSVIP or Bit file for selected FPGA platform

- Complete regression suite containing all the I2C testcases

- Detailed documentation of all functions of perl driver and testcases

- Documentation also contains User's Guide and Release notes

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about Soundwire IP core

MIPI SoundWire v1.2 Boosts Flexibility for Integrating Mobile Audio Interfaces

MIPI SoundWire

MIPI Soundwire: Digital Audio Simplified

MIPI Soundwire IP Sounds Innovative

Breaking the Silence: What Is SoundWire‑I3S and Why It Matters

Frequently asked questions about SoundWire IP cores

What is MIPI SOUNDWIRE PSVIP?

MIPI SOUNDWIRE PSVIP is a Soundwire IP core from SmartDV Technologies listed on Semi IP Hub.

How should engineers evaluate this Soundwire?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this Soundwire IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.