MIPI M-PHY Type 1 G5 2TX2RX - TSMC N7 1.8V, North/South Poly Orientation

The silicon-proven MIPI® M-PHY IP, compliant with the latest MIPI M-PHY v5.0 specification, supports speeds up to 23.32 Gbps per …

Overview

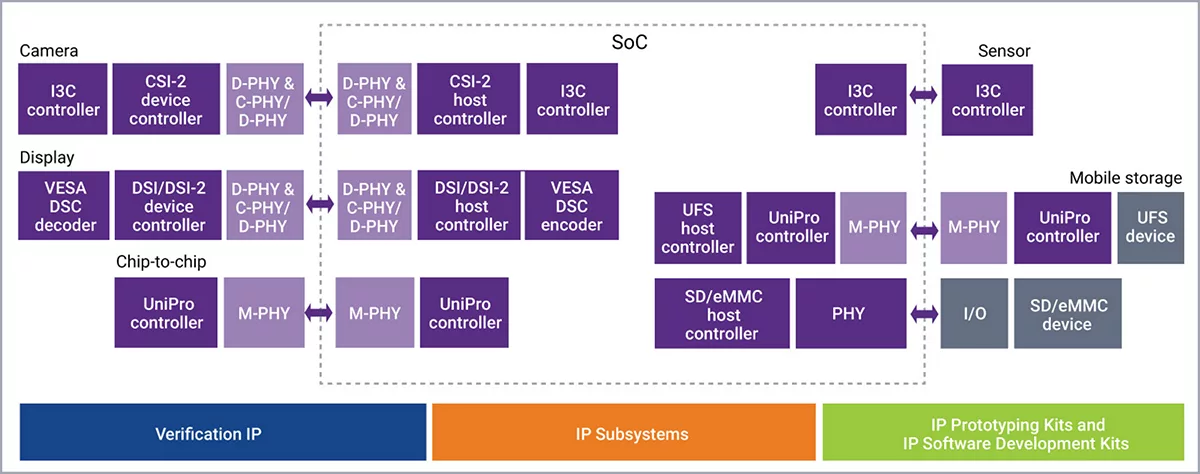

The silicon-proven MIPI® M-PHY IP, compliant with the latest MIPI M-PHY v5.0 specification, supports speeds up to 23.32 Gbps per lane. The IP is optimized for a broad range of high-speed interfaces for applications including JEDEC Universal Flash Storage (UFS) and UniPro interfaces which are widely used in mobile and automotive applications. The M-PHY IP, ideal for embedded storage and chip-to-chip communication, provides low-power features, fast transitions between high-speed burst to low power saving modes, and the ability to manage the TX and RX directions independently.

The MIPI M-PHY IP supports HS Gear1, Gear2, Gear3, Gear4 and Gear5 rates ranging from 1.248 Gbps to 23.32 Gbps per lane. Low-speed capabilities are available with Gear1 to Gear5 PWM modes. A sophisticated clock recovery mechanism and power-efficient clock circuitry are designed to guarantee the integrity of the clocks and signals needed to meet strict timing requirements. The MIPI M-PHY IP supports large and small amplitudes, slew rate control and dithering functionality for optimized electromagnetic interference (EMI).

The MIPI M-PHY IP along with the Universal Flash Storage (UFS) Host Controller IP or the MIPI UniPro Controller IP provides a single vendor UFS IP solution that designers can easily integrate into application processors with less risk, while speeding time-to-market of advanced SoCs and device integrated circuits (ICs).

Key features

- Compliant with MIPI M-PHY v5.0 specification

- Supports MIPI UniPro, JEDEC UFS protocols

- Supports High-Speed (HS) Gear1,

- Gear2, Gear3, Gear4 and Gear5 A/B modes

- Supports M-PHY Type-I

- Modular architecture allows multiple lane configurations

- Low-speed Pulse-Width Modulation (PWM) Gear1 to Gear5 in Type-I LS implementation

- Low-power operation, small area and low latency

- Supports advanced process technologies

- Easily integrates with Synopsys MIPI UniPro and UFS Host

Block Diagram

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| TSMC | 7nm | N7 | — |

Specifications

Identity

Provider

Learn more about MIPI PHY IP core

MIPI DPHY Solution

Infineon Drives Automotive MCU Performance Higher with Synopsys Interface IP

Cadence First to Demo Complete M-PCIe PHY and Controller Solution at MIPI and PCI-SIG Conferences

Super Edge Medical SoC (SEMC)

D-PHY, M-PHY & C-PHY? First Look at Testing MIPI's Latest PHY

Frequently asked questions about MIPI PHY IP

What is MIPI M-PHY Type 1 G5 2TX2RX - TSMC N7 1.8V, North/South Poly Orientation?

MIPI M-PHY Type 1 G5 2TX2RX - TSMC N7 1.8V, North/South Poly Orientation is a MIPI PHY IP core from Synopsys, Inc. listed on Semi IP Hub. It is listed with support for tsmc.

How should engineers evaluate this MIPI PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.