MIPI D-PHY Verification IP

The MIPI D-PHY Verification IP provides an effective & efficient way to verify the components interfacing with MIPI D-PHY interfa…

Overview

The MIPI D-PHY Verification IP provides an effective & efficient way to verify the components interfacing with MIPI D-PHY interface of an IP or SoC. The MIPI D-PHY VIP is fully compliant with MIPI Alliance Specification for D-PHY Version 3.5 This VIP is a light weight VIP with easy plug-and-play interface so that there is no hit on the design cycle time.

Key features

- Compliant to MIPI D-PHY Specification Version 3.5 with PPI interface.

- Support HS-IDLE State between two data burst.

- Support for Alternate calibration Sequence & Preamble sequence.

- Supports all possible configuration for Data Lane Module and Clock Lane Module at PHY layer.

- Supports RAW as well as 8b/9b encoding.

- Supports Special symbols like EoT, Protocol marker, Idle1, Idle2 in case of 8b/9b line encoding.

- Supports for different line states and line levels.

- Configurable numbers of Data lanes.

- Bi-directional data lane turnaround.

- Supported different types of reverse communication.

- Supports configurable control on timing parameters.

- Supports generation and identification of different error scenarios (SoT Error, SoT Sync Error,EoT Sync Error, Escape Entry Command Error, LP Transmission Sync Error, False Control Error).

- Supports dynamically configurable modes.

- Strong Protocol Monitor with real time exhaustive programmable checks.

- Supports Dynamic as well as Static Error Injection scenarios.

- On the fly protocol checking using assertions.

- Built in Coverage analysis.

- Provides a comprehensive user API (callbacks) in Master and Slave.

- Graphical analyzer to show transactions for easy debugging.

- Supports high speed, Escape and Low power control mode.

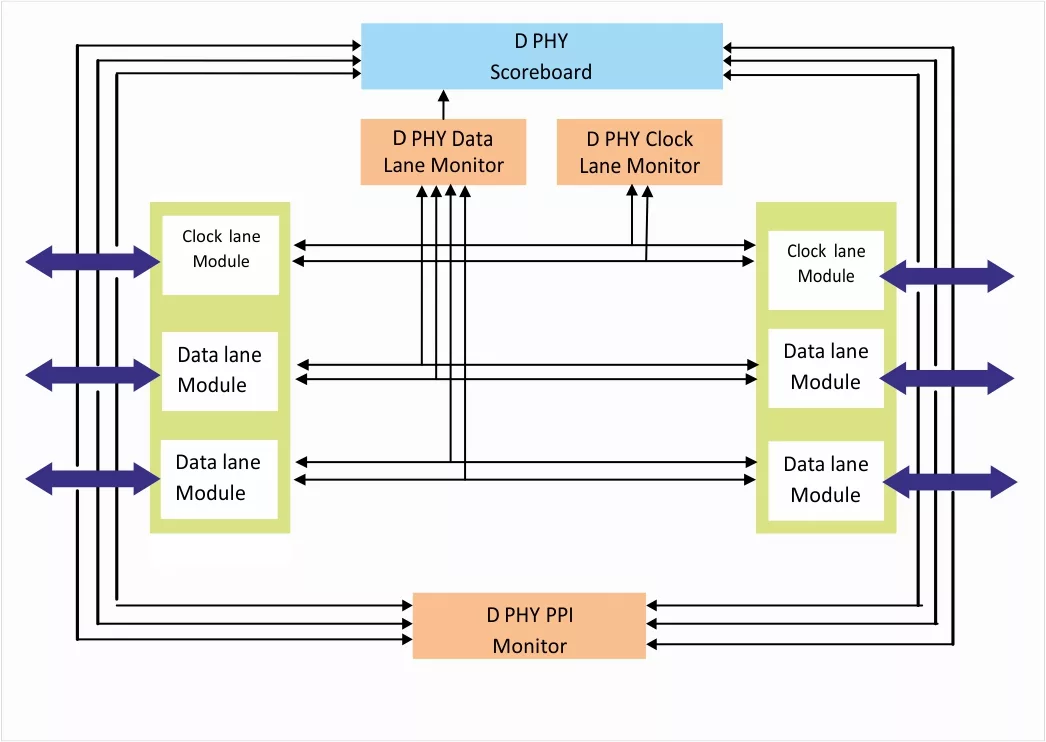

Block Diagram

Benefits

- Available in native System Verilog (UVM/OVM/VMM) and Verilog

- Unique development methodology to ensure the highest levels of quality

- 24X5 customer support

- Unique and customizable licensing models

- Exhaustive set of assertions and coverage points with connectivity examples for all the components

- Consistency of interface, installation, operation, and documentation across all our VIPs

- Provide complete solutions and easy integration in IP and SoC environment

What’s Included?

- MIPI D-PHY Master/Slave BFM/Agent

- MIPI D-PHY Monitor and Scoreboard

- MIPI D-PHY PPI Monitor

- Testbench Configurations

- Test Suite (Available in Source code):

- Basic and Directed Protocol Tests

- Random Tests

- Error Scenario Tests

- Assertions & Cover Point Tests

- Conformance Tests

- Integration Guide, User Manual and Release Notes

Specifications

Identity

Standards & Interfaces

Files

Note: some files may require an NDA depending on provider policy.

Provider

- To create world class Verification IP Solutions

- To provide expert consultancy to ASIC & SoC Design companies

- To design SOCs from Architecture to Working Silicon

- To be the leading provider of Semiconductor IP Solutions

- To be a one-stop-shop for Design and Verification

- Customer Success

- Commitment to Quality

- Quality of Products

- Quality of Engineers

- Best in class Customer Support

- Ethics and Integrity

Learn more about MIPI PHY IP core

MIPI DPHY Solution

Infineon Drives Automotive MCU Performance Higher with Synopsys Interface IP

Cadence First to Demo Complete M-PCIe PHY and Controller Solution at MIPI and PCI-SIG Conferences

Super Edge Medical SoC (SEMC)

D-PHY, M-PHY & C-PHY? First Look at Testing MIPI's Latest PHY

Frequently asked questions about MIPI PHY IP

What is MIPI D-PHY Verification IP?

MIPI D-PHY Verification IP is a MIPI PHY IP core from Truechip Solutions listed on Semi IP Hub.

How should engineers evaluate this MIPI PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.