MIPI C-PHY/D-PHY Combo IP

The MIPI C/D-PHY combo IP is a high-frequency low-power, low cost, physical layer compliant with the MIPI® Alliance Standard for …

Overview

The MIPI C/D-PHY combo IP is a high-frequency low-power, low cost, physical layer compliant with the MIPI® Alliance Standard for C-PHY and D-PHY.

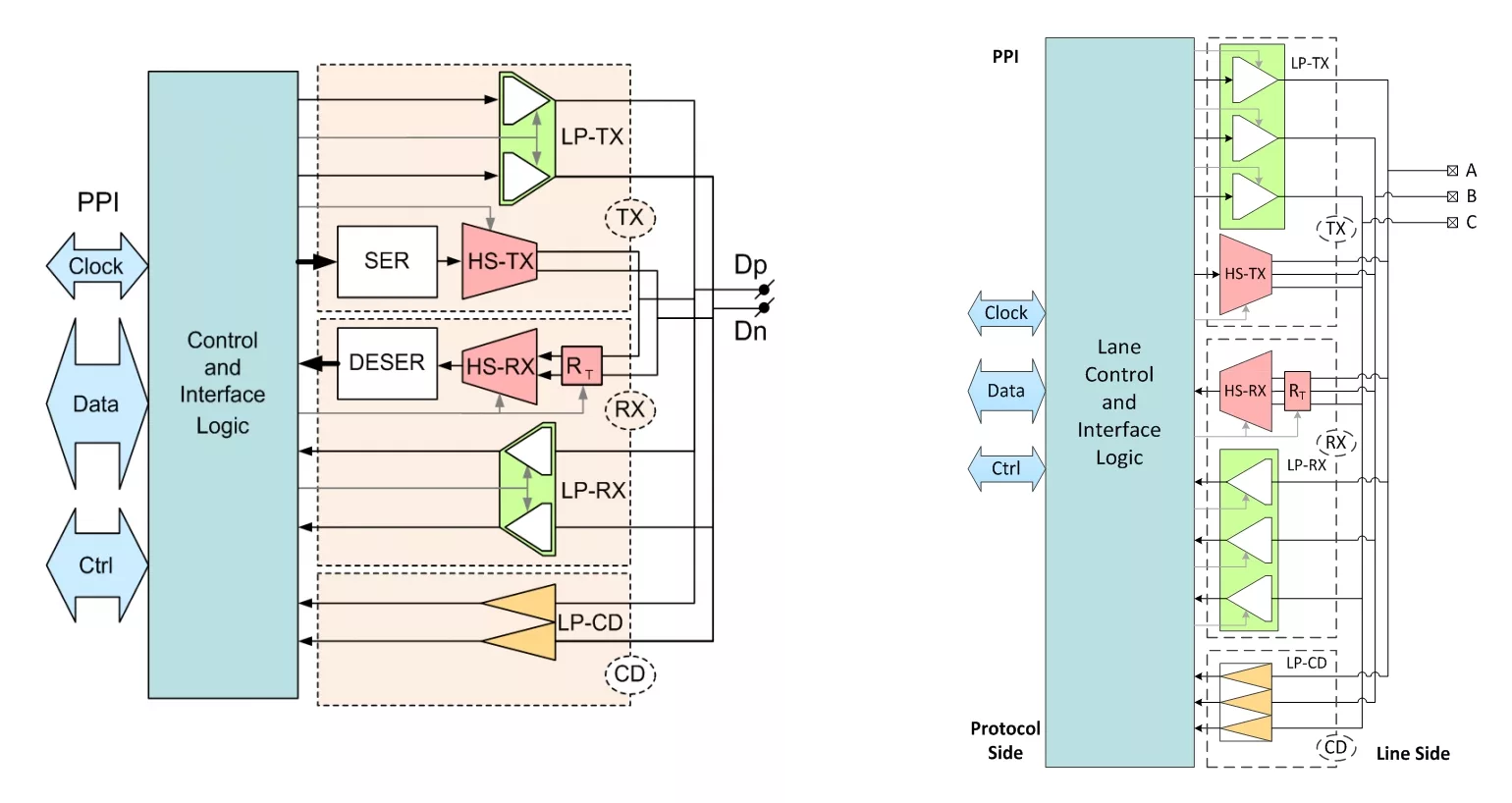

The PHY can be configured as a MIPI Master or MIPI Slave, supporting camera interface CSI-2 v1.2 or display interface DSI v1.3 applications in the D-PHY mode. It also supports camera interface CSI-2 v1.3 and display interface DSI-2 v1.0 applications in the C-PHY mode. The high-speed signals have a low voltage swing, while low-power signals have large swing. High-Speed functions are used for high-speed data traffic while low-power functions are mostly used for control.

The C-PHY is based on 3-Phase symbol encoding technology, delivering 2.28 bits per symbol over three-wire trios, operating with a symbol rate range of 80 to 4500 Msps per lane, which is the equivalent of about 182.8 to 10260 Mbps per lane.

The D-PHY supports a bit rate range of 80 to 1500 Mbps per Lane without deskew calibration, and up to 4500 Mbps with deskew calibration.

The low-power mode and escape mode are the same in both the D-PHY and C-PHY modes. To minimize EMI, the drivers for low-power mode are slew-rate controlled and current limited. The data rate in low-power mode is 10 Mbps. For a fixed clock frequency, the available data capacity of a PHY configuration can be increased by using more lanes. Effective data throughput can be reduced by employing burst mode communication.

The C-PHY/D-PHY combo is a complete PHY, silicon-proven at multiple foundries and multiple nodes. The C/D-PHY is fully integrated and has analog circuitry, digital, and synthesizable logic.

Key features

- Dual mode PHY can support C-PHY and D-PHY

- Supports MIPI® D-PHY Specification Version 2.5 with backwards compatibility for v2.1, v1.2, and v1.1

- Supports MIPI C-PHY Specification Version 2.0 with backwards compatibility for v1.1 and v1.2

- Four lanes in D-PHY mode and three lanes in C-PHY mode

- Supports both high-speed and low-power modes

- 80 Mbps to 1.5 Gbps data rate per lane in D-PHY mode without deskew calibration

- Up to 4.5 Gbps data rate per lane in D-PHY mode with deskew calibration

- 80 Msps to 4.5 Gsps symbol rate per lane in C-PHY high-speed mode

- Equivalent to 182.8 Mbps to 10.26 Gbps per lane in C-PHY high-speed mode

- 10 Mbps data rate in low-power mode

- Low power dissipation

- Loopback testability (BIST) support

- Optional resistance termination calibrator

- Deskew calibration support in D-PHY

Block Diagram

Benefits

- Area overhead is minimized by reusing all of the D-PHY blocks for the C-PHY operation and sharing of all the serial interface pins

- Comprehensive embedded DFT features for allowing cost-effective high-volume manufacturing tests

- Support for full-speed internal loopback testability with minimal area overhead for high-volume manufacturing tests in the C/D-PHY Universal, TX+, and RX+ configurations

- Support for MIPI D-PHY v2.5 and MIPI C-PHY v2.0 features not available in previous versions of the specifications such as Spread Spectrum Clocking (SSC) and transmit equalization (de-emphasis)

- Support for new power saving functionality such as HS-TX half swing mode and HS-RX unterminated mode

- Support for new Alternate LP Mode, suitable for IoT applications with long channels, enabling Fast Bus Turnaround

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about MIPI PHY IP core

MIPI DPHY Solution

Infineon Drives Automotive MCU Performance Higher with Synopsys Interface IP

Cadence First to Demo Complete M-PCIe PHY and Controller Solution at MIPI and PCI-SIG Conferences

Super Edge Medical SoC (SEMC)

D-PHY, M-PHY & C-PHY? First Look at Testing MIPI's Latest PHY

Frequently asked questions about MIPI PHY IP

What is MIPI C-PHY/D-PHY Combo IP?

MIPI C-PHY/D-PHY Combo IP is a MIPI PHY IP core from Mixel, Inc. listed on Semi IP Hub.

How should engineers evaluate this MIPI PHY?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this MIPI PHY IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.