Microsecond Channel (MSC/MSC-Plus) Controller

The MSC-CTRL IP core implements a high-speed serial interface controller designed to connect a microcontroller or SoC to external…

Overview

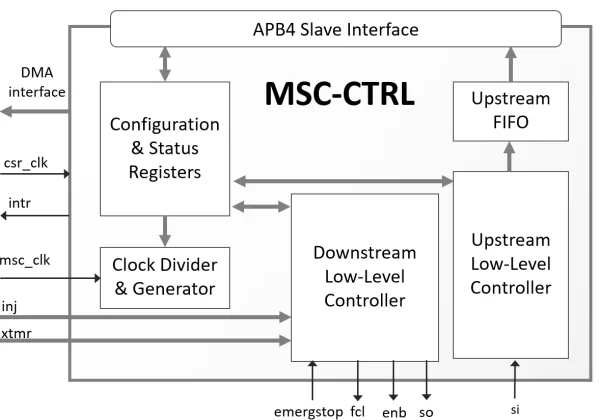

The MSC-CTRL IP core implements a high-speed serial interface controller designed to connect a microcontroller or SoC to external power devices or sensors. It implements the Microsecond Channel (MSC) and Microsecond Channel Plus (MSC-Plus) protocols—derived from the Microsecond Bus (uSB) serial concept—and acts as a bus master for downstream transmission and as a bus slave for upstream transmission.

The MSC-CTRL connects microcontrollers to peripheral devices via high-speed synchronous downstream and low-speed asynchronous upstream channels. It supports up to four slave devices in the MSC mode, while MSC-Plus is optimized for one-to-one communication with a single slave device. Advanced features, including Manchester encoding, fragmented command frames, and higher upstream baud rates, provide robust communication in a network of dedicated sensors or devices.

The controller’s communication with the host processor is facilitated by a 32-bit AMBA® APB4 subordinate interface. The MSC-CTRL features trigger signals to facilitate easy integration with an external DMA controller and a comprehensive set of interrupt sources for reporting status and error information.

The silicon-proven MSC-CTRL core is designed to industry best practices and has been rigorously verified. Available functional safety documents facilitate ISO 26262 ASIL B certification.

Key features

Supported Protocols

- MSC de-facto standard as used by Infineon, Renesas & other devices

- MSC-Plus per Bosch Requirement Specification v2.23

- Microsecond Bus (uSB) per SAE 2005-01-0057

- The core is not intended as a minimal uSB controller

MSC 2nd Generation

- Up to 4 enable lines for four peripheral devices

- Downstream channel high-speed synchronous transmission

- Command or data frame types

- 32/64-bit data frames extension

- Emergency stop input without CPU intervention

- Upstream channel low-speed asynchronous reception

- Diagnostic error codes

- Programmable data frame length (12/16-bit) and delay of the receive interrupt

- 8-to-1 input multiplexer for SI lines

- Parity error checker

MSC-Plus

- Manchester encoding

- Flexible Frame with combined Command and data

- One-to-one connection with slave device

- Up to 64-bit payload

- Downstream Channel

- Programmable repetition period

- Upstream Channel

- Timeout detection

Ease of Integration

- Programmable spike/glitch filter

- Repetition or Triggered Downstream Transfer modes

- 32-bit APB4 subordinate interface

- DMA support via trigger signals:

- Start of downstream data and command transmission

- End of downstream command transmission

- Upstream new data reception

- Configurable upstream frame DMA triggers

- Register/Memory Parity Check

- Comprehensive Set of Interrupts for communication & safety events

- LINT-clean with clean clock-domain crossing boundaries

Block Diagram

What’s Included?

- A sophisticated self-checking SystemVerilog testbench

- Simulation scripts, test vectors, and expected results

- Sample synthesis scripts and constraint files

- IP-XACT register definitions

- Comprehensive user documentation

- An ISO 26262 ASIL-B certification package—comprising a Safety Manual (SAM), FMEDA, and FMEA documents—is deliverable on request

Files

Note: some files may require an NDA depending on provider policy.

Specifications

Identity

Provider

Learn more about IEEE-1588 / PTP IP core

Frequently asked questions about Time Synchronization IP cores

What is Microsecond Channel (MSC/MSC-Plus) Controller?

Microsecond Channel (MSC/MSC-Plus) Controller is a IEEE-1588 / PTP IP core from CAST listed on Semi IP Hub.

How should engineers evaluate this IEEE-1588 / PTP?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this IEEE-1588 / PTP IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.