Low Power All Digital Fractional-N PLL in GlobalFoundries 22FDX

The DeepSub™ pPLL05F is a low power, low voltage all digital PLL featuring low-jitter and compact area.

Overview

The DeepSub™ pPLL05F is a low power, low voltage all digital PLL featuring low-jitter and compact area. It is suitable for IoT and embedded clocking applications in systems running below the nominal core voltage at frequencies up to 1.0GHz. It is suitable as a clock source for moderate speed microprocessor blocks and other logic.

To give IoT designers the maximum flexibility in managing power, pPLL05F is very small (< 0.01 sq mm) and low power (< 1.0mW). It is well suited to applications with a single low voltage power supply that the PLL shares with the blocks that use its output clock. Better jitter performance can be achieved if the pPLL05F has its own analog power supply.

pPLL05F integrates easily into any SoC design and includes all the views and models required by back end flows.

The pPLL05F is built using Perceptia’s second generation all digital PLL technology. This robust technology delivers identical performance across many processes, regardless of PVT conditions. It consumes a small fraction of the area of an analog PLL whilst maintaining comparable performance.

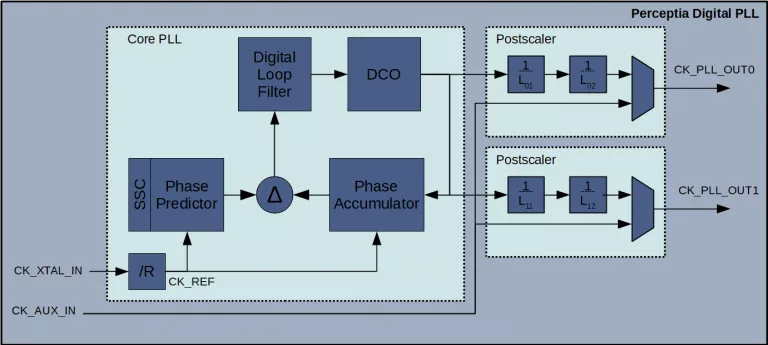

pPLL05F can be used as an integer-N PLL or as a fractional-N PLL. The fractional-N mode provides a high flexibility to choose the best combination of input and output clock frequencies at the system level.

Perceptia further provides integration support and offers customization and migration services.

Key features

- Low power, suitable for IoT applications

- Good jitter, suitable for clocking digital logic.

- Extremely small die area (< 0.01 sq mm), using a ring oscillator

- Output frequency can be from 1 to 200 times the input reference, up to 1.0GHz

- Reference clock from 5MHz to 200MHz

- Second-generation digital PLL architecture, providing integer and fractional multiplication

- Two PLL outputs via separate postscalers

- Post-scalers programmable from 1 to 2,040

- Lock-detect output

- Can generate a spread-spectrum clock from a clean reference

- Oscillator output duty cycle better than 48 / 52%

- Highly testable using industry standard flows

- ATPG vectors provided

- Specification of functional tests to supplement ATPG testing

Block Diagram

Benefits

- Small size (< 0.01 sq mm)

- Low Power (< 1.0mW)

- Easy integration

- Fractional Multiplication

Applications

- IoT

- Embedded

- Moderate speed digital systems

What’s Included?

- Datasheet

- Detailed Verilog behavioral model

- Timing models

- LEF5.6 abstract for floor planning/chip assembly

- Integration Guide

- DFT Guide

- Integration support

- Characterization report

- GDSII layout macrocell

- CDL netlist for LVS

- DRC, LVS and SI verification reports

- Netlist model with accompanying documentation allowing integration of the module in scan chains

Files

Note: some files may require an NDA depending on provider policy.

Silicon Options

| Foundry | Node | Process | Maturity |

|---|---|---|---|

| GlobalFoundries | 22nm | FDX | — |

Specifications

Identity

Provider

Learn more about PLL IP core

CoreHW Develops 80GHz mmWave PLL with Synopsys RFIC Design Flow on GlobalFoundries 22FDX Technology

Specifying a PLL Part 3: Jitter Budgeting for Synthesis

Specifying a PLL Part 2: Jitter Basics

Specifying a PLL Part 1: Calculating PLL Clock Spur Requirements from ADC or DAC SFDR

Achieving Groundbreaking Performance with a Digital PLL

Frequently asked questions about PLL IP cores

What is Low Power All Digital Fractional-N PLL in GlobalFoundries 22FDX?

Low Power All Digital Fractional-N PLL in GlobalFoundries 22FDX is a PLL IP core from Perceptia Devices listed on Semi IP Hub. It is listed with support for globalfoundries.

How should engineers evaluate this PLL?

Engineers should review the overview, key features, supported foundries and nodes, maturity, deliverables, and provider information before shortlisting this PLL IP.

Can this semiconductor IP be compared with similar products?

Yes. Buyers can compare this product with similar semiconductor IP cores or IP families based on category, provider, process options, and structured technical specifications.